| Summary SIEMENS The 7 Challenges of Embedded Software Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

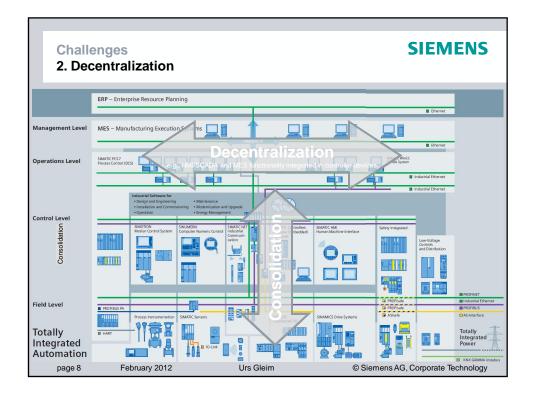

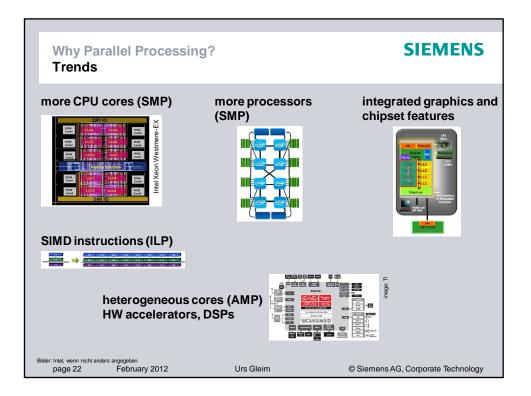

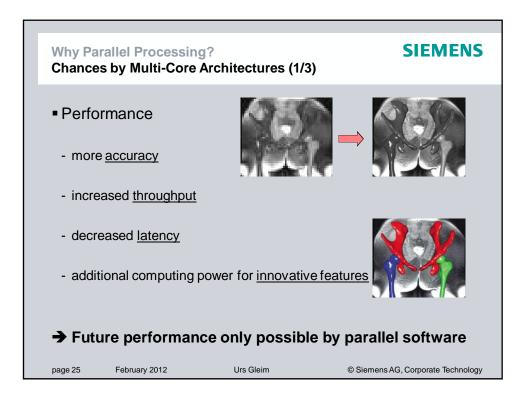

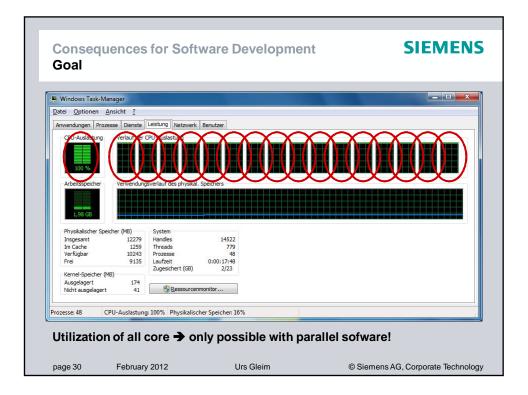

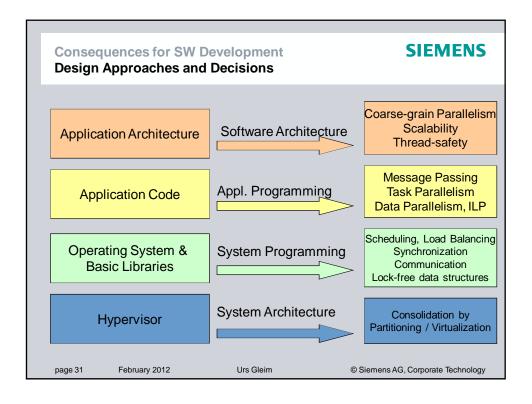

| <ul> <li><b>1. Consolidation</b> <ul> <li>shift from HW to SW</li> <li>utilization of multi-/many-core systems</li> <li>taking into account safety and real-time requirements</li> </ul> </li> <li><b>2. Decentralization</b> <ul> <li>flexible deployment of functionality in distributed systems</li> </ul> </li> <li><b>3. Heterogeneity</b> <ul> <li>heterogeneous multi-/many-core architectures</li> <li>hardware accelerators</li> <li>cloud computing</li> </ul> </li> <li><b>4. Security</b> <ul> <li>data privacy</li> <li>protection against manipulation</li> </ul> </li> </ul> | <ul> <li>5. Energy management <ul> <li>power-efficient hard- and software</li> </ul> </li> <li>6. Programming models <ul> <li>Development efficiency and future-proofness</li> <li>Portability, HW-independence</li> <li>Scalability with processing power (more cores)</li> </ul> </li> <li>7. Migration strategies <ul> <li>utilize parallel hardware preserving existing code bases</li> </ul> </li> </ul> |  |  |  |

| page 14 February 2012 Urs Gleim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | © Siemens AG, Corporate Technology                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

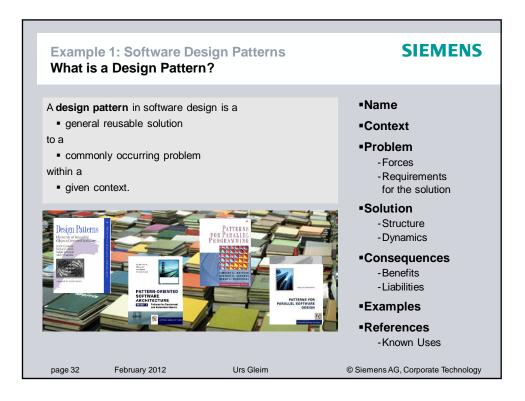

| Example 1: Software<br>Concurrency Pattern                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                           | SIEMENS                                                                                                                                                                                                                   |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <ul> <li>Architectural Patterns <ul> <li>Asynchronous<br/>Agents</li> <li>Parallel Tasks</li> <li>Repository</li> <li>Irregular Mesh</li> </ul> </li> <li>Algorithm Patterns <ul> <li>Divide &amp; Conquer</li> <li>Parallel Pipes &amp;<br/>Filters</li> <li>Geometric<br/>Decomposition</li> <li>Recursive Data</li> </ul> </li> </ul> | Concurrency Patterns <ul> <li>Half-Sync/Half-Asynd</li> <li>Leader/Followers</li> <li>Active Object</li> <li>Monitor Object</li> <li>Thread Specific Storage</li> </ul> <li>Program Structuring Patterns <ul> <li>SPMD</li> <li>Master/Worker</li> <li>Loop Parallelism</li> <li>Fork/Join</li> </ul> </li> | Data Sharing Patterns<br>Shared Data<br>Shared Queue<br>Replicable<br>Synchronization Patterns<br>Thread-Safe Interface<br>Double-Checked<br>Locking<br>Strategized Locking<br>Strategized Locking<br>Proactor<br>Reactor |  |  |

| POSA2 Mattson et al.                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                           |  |  |

| page 33 February 2012                                                                                                                                                                                                                                                                                                                    | Urs Gleim                                                                                                                                                                                                                                                                                                   | © Siemens AG, Corporate Technology                                                                                                                                                                                        |  |  |

| Example 1: Software Design Patterns SIEMENS<br>Concurrency Patterns == Multicore Patterns?                                                                           |                                                                                                                                                                                                                                                                                        |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| WE HAVE                                                                                                                                                              | BUT                                                                                                                                                                                                                                                                                    |  |  |  |

| <ul> <li>Classic concurrency patterns</li> <li>Origin: server applications</li> <li>→ many users</li> <li>→ small tasks that are more or less independent</li> </ul> | <ul> <li>Multicore aspects not addressed</li> <li>Scalability with number of cores</li> <li>Memory hierarchy</li> <li>Parallel programming models</li> </ul>                                                                                                                           |  |  |  |

| <ul> <li>Parallel algorithms</li> <li>Scientific computations, high performance computing</li> <li>Image processing (data parallel algorithms)</li> <li></li> </ul>  | <ul> <li>Patterns Missing <ul> <li>Only a few best practices are documented as design patterns; missing for example:</li> <li>Patterns for task parallelism,</li> <li>Speculative execution on application level,</li> <li>Effective parallel stream processing</li> </ul> </li> </ul> |  |  |  |

| page 34 February 2012 Urs                                                                                                                                            | s Gleim © Siemens AG, Corporate Technology                                                                                                                                                                                                                                             |  |  |  |

| Example<br>Conclus                                                                                                                                                                                            | e 1: Software De<br>sion | sign Patterns | SIEMENS                            |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------|------------------------------------|--|

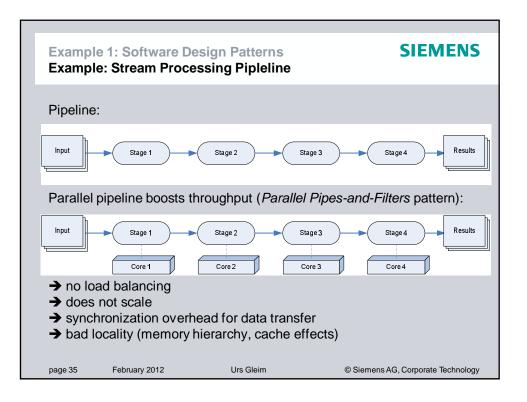

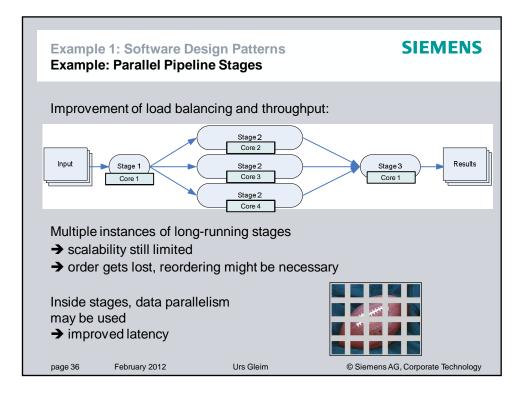

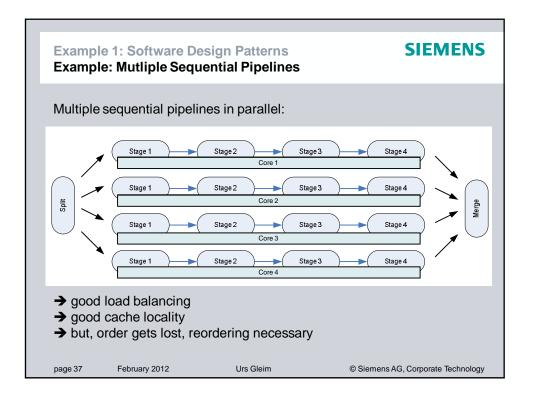

| <ul> <li>Find a scalable partitioning of the problem</li> <li>Architecture should support load balancing</li> <li>Parallelism should be scalable with number of cores</li> <li>Avoid waiting times</li> </ul> |                          |               |                                    |  |

| <ul> <li>→ Keep data local</li> <li>bad locality can slow down an application massively<br/>(costs for data transfer, false sharing)</li> <li>No complicated architecture needed</li> </ul>                   |                          |               |                                    |  |

| <ul> <li>Parallel execution can change the processing order</li> <li>Only possible if no dependencies between data elements</li> <li>Additional effort for restoring order</li> </ul>                         |                          |               |                                    |  |

| page 38                                                                                                                                                                                                       | February 2012            | Urs Gleim     | © Siemens AG, Corporate Technology |  |