Events 2023

Best Paper Award at MEMOCODE'23, September 21-22, 2023, Hamburg

The paper "Hybrid Genetic Reinforcement Learning for Generating Run-Time Requirement Enforcers" (Jan Spieck, Pierre-Louis Sixdenier, Khalil Esper, Stefan Wildermann and Jürgen Teich) has won the Best Paper Award at ESWEEK 2023's 21st ACM-IEEE International Symposium on Formal Methods and Models for System Design (MEMOCODE) in Hamburg, Germany. In their work, the authors propose a novel design space exploration methodology that uses a combination of evolutionary algorithms and reinforcement learning to efficiently find verifiable feedback-based controllers for non-functional requirements such as latency or energy. The approach is shown to significantly reduce exploration time and to outperform existing methods in generating controllers with higher probabilities of meeting verification goals in three case studies. The paper originated as part of TRR 89 Invasive Computing.

Jan Spieck, Pierre-Louis Sixdenier, Khalil Esper, Stefan Wildermann and Jürgen Teich have received the Best Paper Award at MEMOCODE'23 (Photo: FAU/Andreas Bininda)

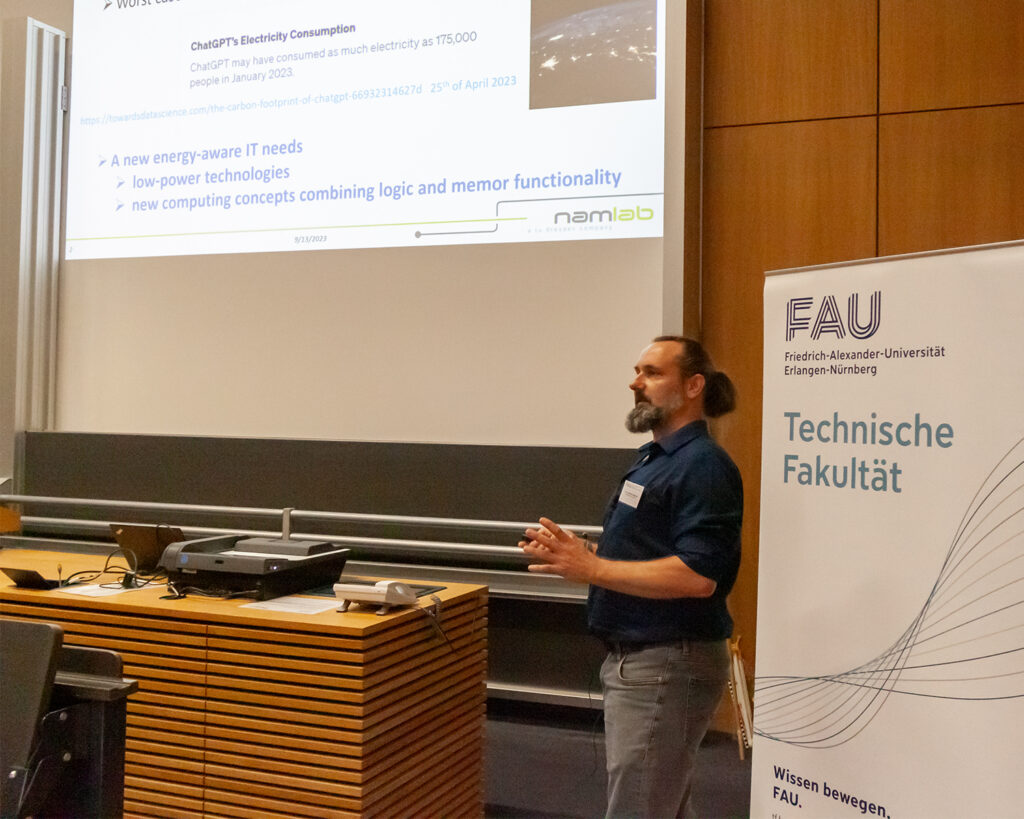

Embedded Talk "Non-volatile memory technologies and applications", September 13, 2023, DAU

On Wednesday, September 13, 2023, the 16th Embedded Talk was held for the first time again in presence at FAU in Erlangen. The topic was "Non-volatile memory technologies and applications". Many participants took the opportunity to exchange information about current research and developments in this field. After a welcome by ESI speaker Prof. Dr.-Ing. Jürgen Teich, Dr.-Ing. Stefan Slesazeck (Senior Scientist at NaMLab gGmbH, Dresden) started with his keynote on "Ferroelectric memories for neuromorphic computing". Afterwards, Prof. Dr.-Ing. Christian Hochberger (Chair for Computer Systems, TU Darmstadt) addressed memristor-based FPGAs and their opportunities and risks in his keynote. Inspired by the exciting keynotes and refreshed by a coffee break, panel discussion moderated by Prof. Dr.-Ing. Jürgen Teich introduced the interactive part of the event. In addition to the two keynote speakers, Prof. Dr.-Ing. Dietmar Fey (FAU) also participated in the discussion on the podium. The lively discussions then continued during the poster session, where 8 exhibitors from the two DFG priority programs SPP 2262 ("Memristive Devices for Intelligent Technical Systems") and SPP 2377 ("Disruptive Main Memory Technologies") reported on their projects. For some of the participants, it was their first exchange with researchers from the other DFG SPP. Thus, the event provided important networking opportunities especially for PhD students from FAU ESI.

Prof. Teich welcoming the guests (Photo: FAU/Andreas Bininda)

Keynote speaker Dr. Slezazeck, NaMLab gGmbH (Photo: FAU/Andreas Bininda)

Prof. Teich moderating the Panel Discussion with Prof. Hochberger, Prof. Fey and Dr. Slesazeck (Photo: FAU/Andreas Bininda)

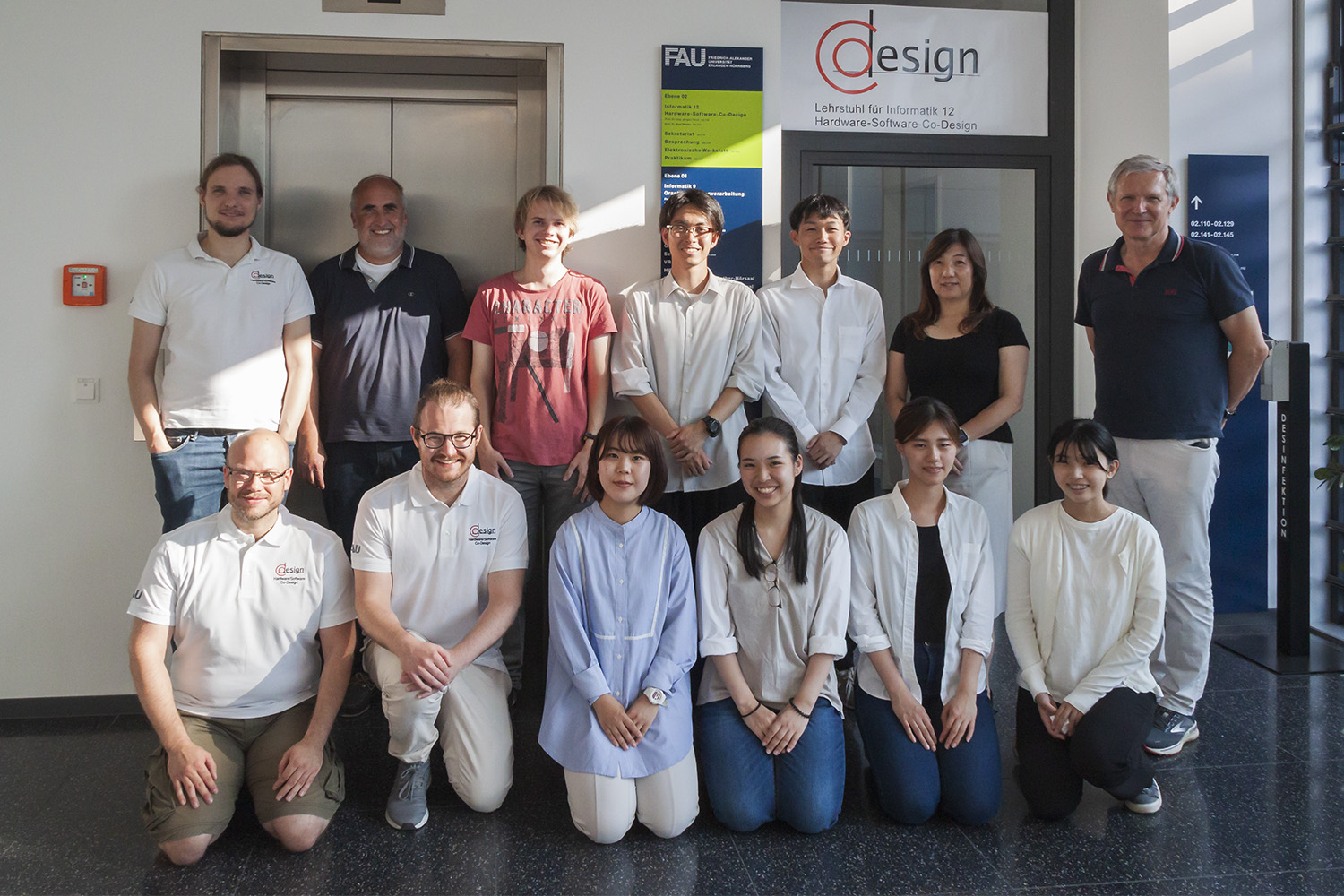

Student delegation from Osaka University, Japan, visiting FAU, September 11-12, 2023

On September 11 and 12, a group of selected delegates studying in various engineering programs at Osaka University, FAU's partner university, visited Erlangen. The visit was coordinated by Prof. Kiyoshi Fujita, Director of the Center for International Relations of the Graduate School of Engineering, and Ms. Ikuko Nojiri. The group was hosted by the Chair of Computer Science 12 (Hardware-Software-Co-Design) of Prof. Jürgen Teich. Thanks also to Daniel Seidel, a student of computer science at FAU, for his help in also coordinating the visit. Mr. Seidel was able himself to enjoy a stay at Osaka University during the past semester as part of the Maple exchange program.

Student delegation from Osaka University visiting the Chair of Computer Science 12

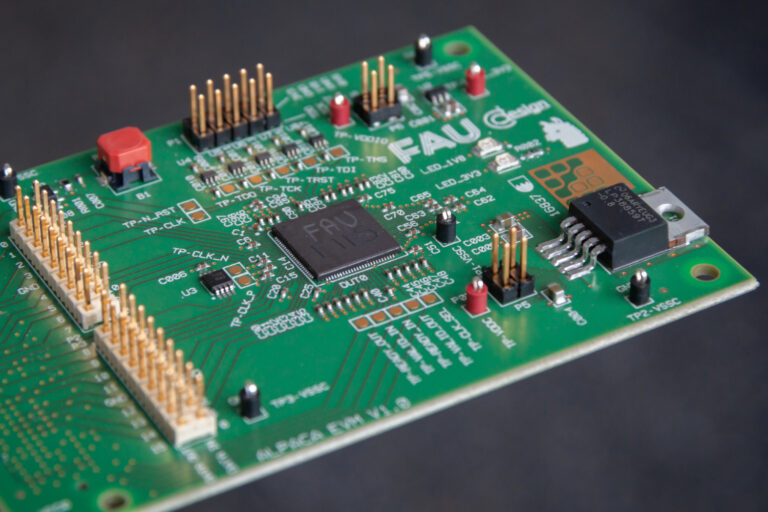

Hardware/Software Co-Design Team designs Supercomputer-on-a-Chip

A team of the Hardware/Software Co-Design Chair designed a chip that integrates 64 custom processor cores.

A board for testing the developed chip. Picture: FAU/Andreas Bininda

The chip, called ALPACA, unleashes an enormous computing power of up to 384 billion arithmetic operations per second while drawing less than 3 watts. ALPACA’s application domains are manifold. The chip is suitable for the fast processing of digital signals (audio, video) as well as large amounts of data, such as those present in machine learning and scientific computing. Thanks to its low power demands, applications in the fields of medical technology, IoT systems, and automotive benefit in particular. ALPACA was developed within the Collaborative Research Centre/Transregio 89 “Invasive Computing,” funded by the German Research Foundation (DFG). The area of the chip is just 10 mm2, manufactured in 22 nm semiconductor technology. However, a chip is only as powerful as its corresponding compilation and programming tools. Therefore, in a unique hardware/software co-design, a powerful compiler for parallelization and automatic mapping of loop programs has been developed parallel to the chip design.

The developer team. Picture: FAU/Andreas Bininda

EDAA Outstanding Dissertation Award, DATE 2023, April 18, 2023, Antwerp

Dr.-Ing. Martin Rapp (KIT)

Martin Rapp, has received the EDAA Outstanding Dissertation Award 2023 at DATE 2023 for his outstanding dissertation entitled "Machine Learning for Resource-Constrained Computing Systems".

DATE 2023 Party Award Session, April 18, 2023, Antwerp

Prof. Dr.-Ing. Jürgen Teich (FAU)

Professor Jürgen Teich was awarded the DATE Fellow Award at the Award Session of the Design Automation & Test in Europe (DATE) conference 2023. He has received this award for distinguishing himself in the DATE organization team over many years, especially for his leadership role as General Chair of DATE 2019 in Florence.

Prof. Dr.-Ing. Jürgen Teich reveiving his DATE Fellow Award, Copyright DATE, Cruz Garcia

Opening Ceremony Session DATE 2023, April 17, 2023, Antwerp

Prof. Dr.-Ing. Jürgen Teich (FAU)

Professor Teich presented several prestigious EDA (Electronic Design Automation) awards as Awards Chair at the Design Automation & Test in Europe (DATE) conference 2023.

Prof. Dr.-Ing. Jürgen Teich at the Opening Ceremony Session, Copyright DATE, Cruz Garcia

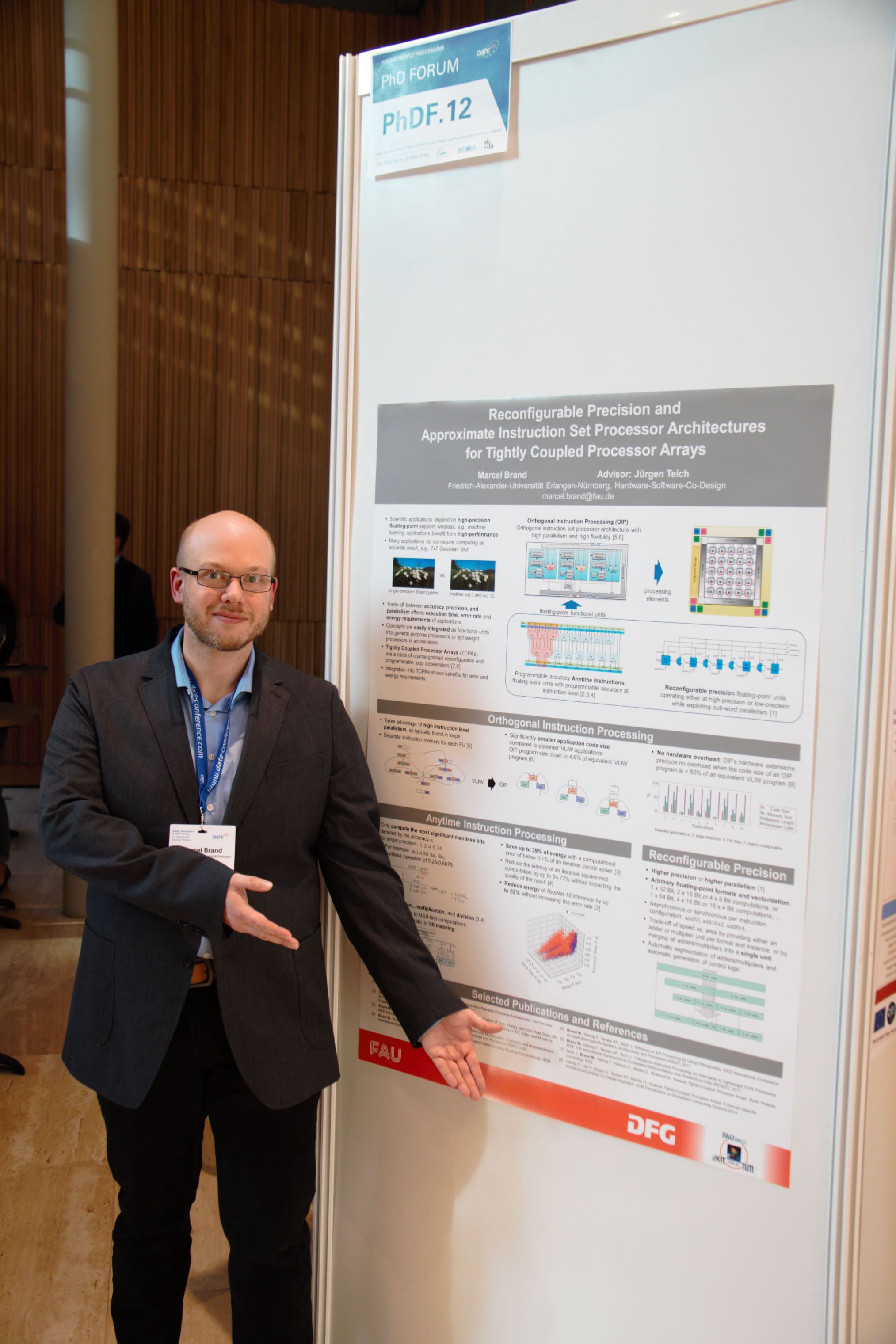

PhD Forum DATE 2023, April 17, 2023, Antwerp

Marcel Brand (FAU)

Marcel Brand presented his research results with a poster at the PhD Forum at the Design Automation & Test in Europe (DATE) conference 2023 in Antwerp. The conference was held in presence for the first time since 2019. Many attendees were interested to learn about his work and innovative processor architecture concepts for processor arrays.

Marcel Brand presenting his poster at the DATE 2023 PHD Forum

Events 2022

Best Paper Award at SBESC'22,November 21-24,2022, Fortaleza, Brasilien

Benedikt Jung, Christian Eichler, Jonas Röckl, Ralph Schlenk, Prof. Dr.-Ing. Timo Hönig, Prof. Dr.-Ing. Tilo Müller

Timo Hönig (RUB) and his research group received a Best Paper Award for the work "Trusted Monitor: TEE-Based System Monitoring" at the XII Brazilian Symposium on Computing Systems Engineering (SBESC'22).

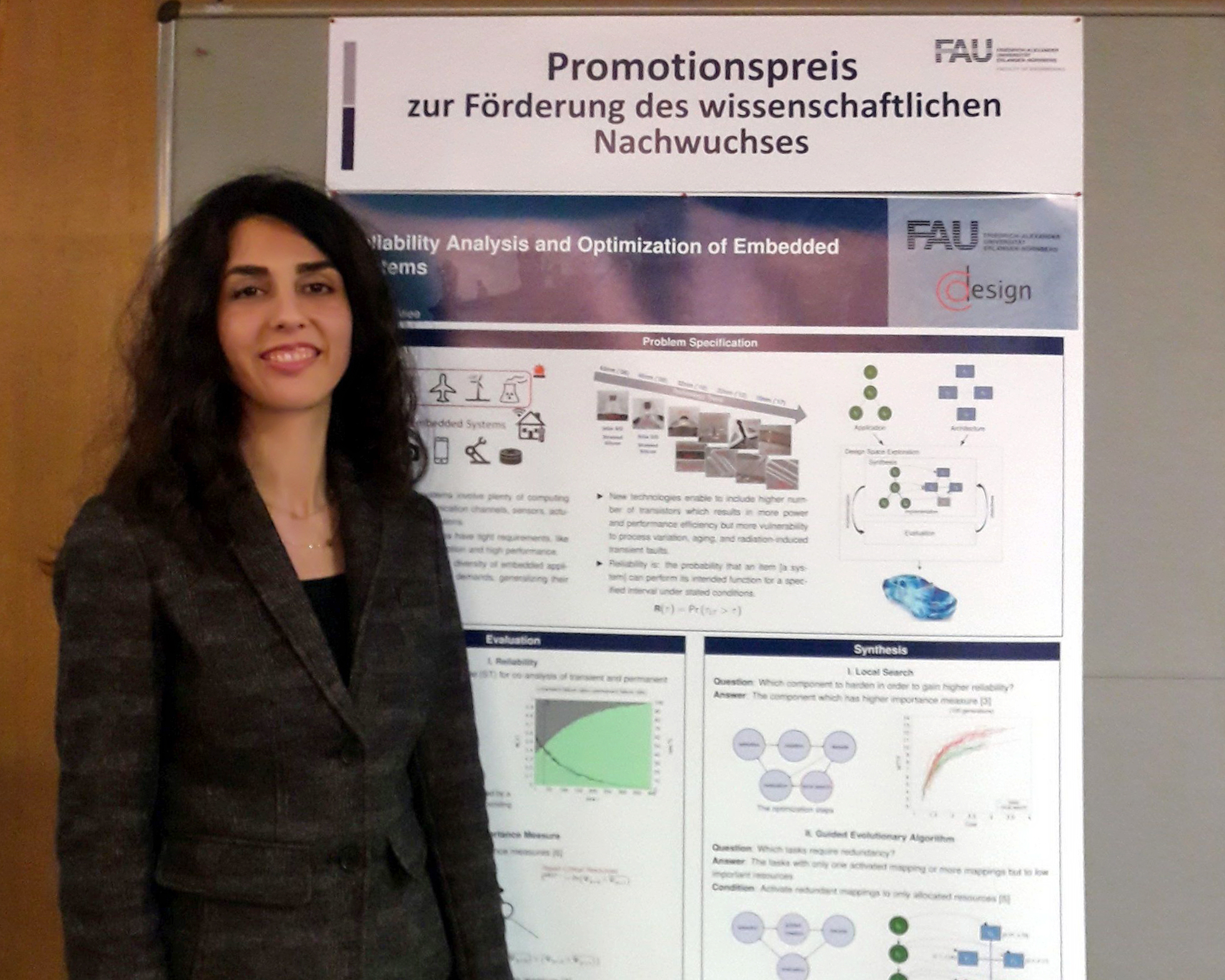

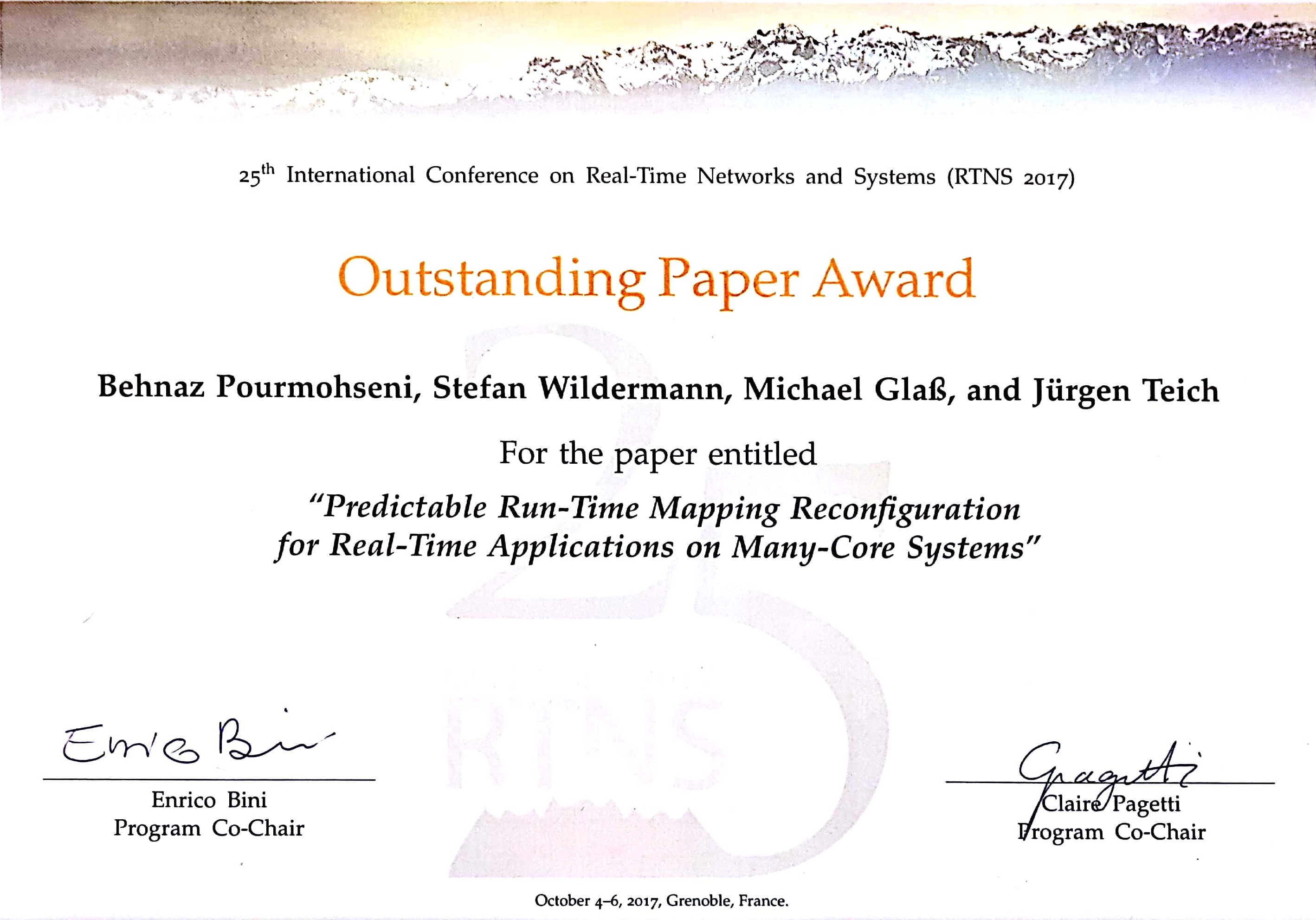

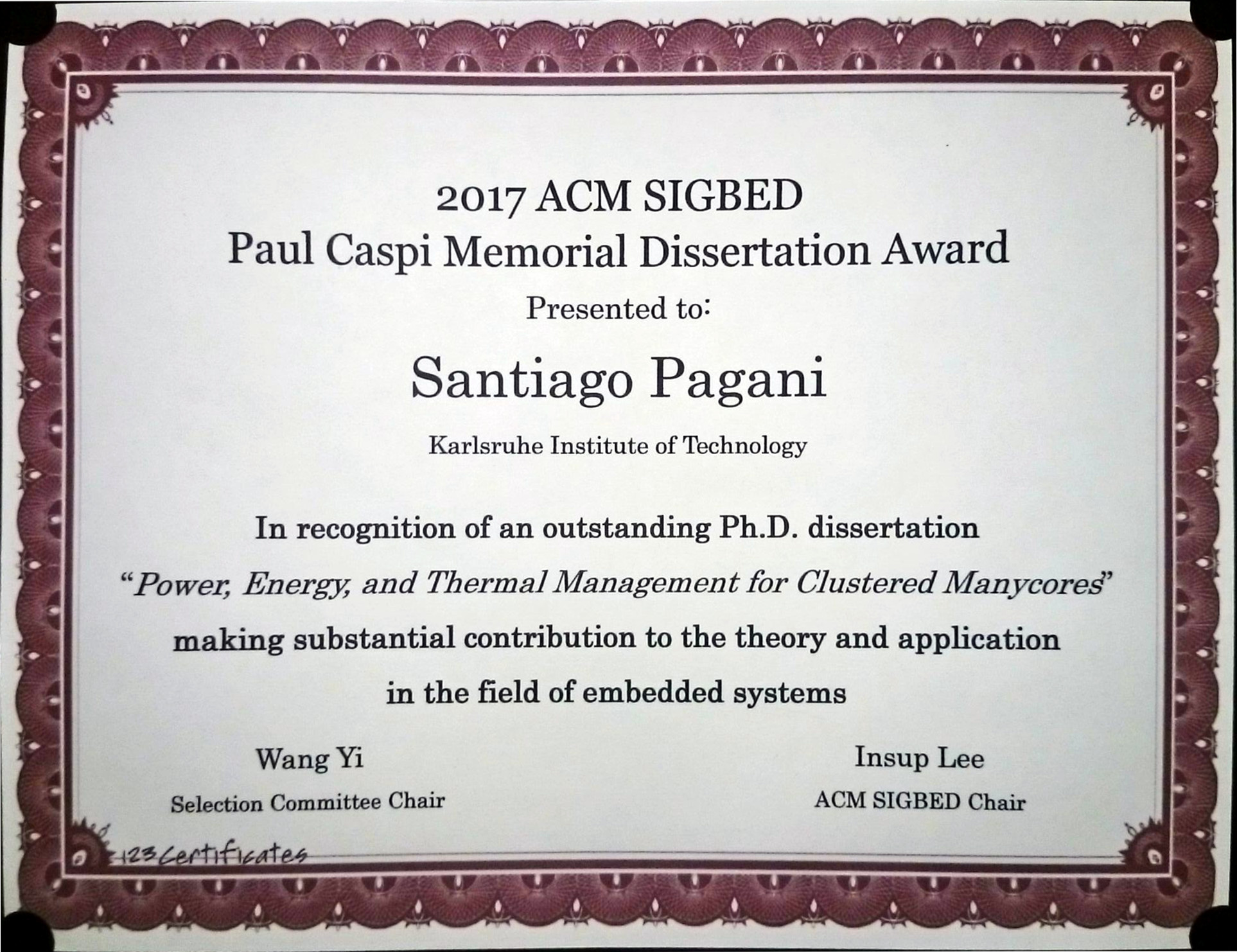

Dissertation Award for Dr.-Ing. Behnaz Pourmohseni,November 18,2022, Erlangen

Dr.-Ing. Behnaz Pourmohseni (FAU)

At the occasion of the Day of the Faculty of Engineering 2022, Mrs. Behnaz Pourmohseni is awarded the ATE Alumni Dissertation Award for her thesis "System-Level Mapping, Analysis, and Management of Real-Time Applications in Many-Core Systems".

Dr.-Ing. Behnaz Pourmohseni receiving her Dissertation Award

InvasIC Colloquium, October 6-7, 2022, Erlangen

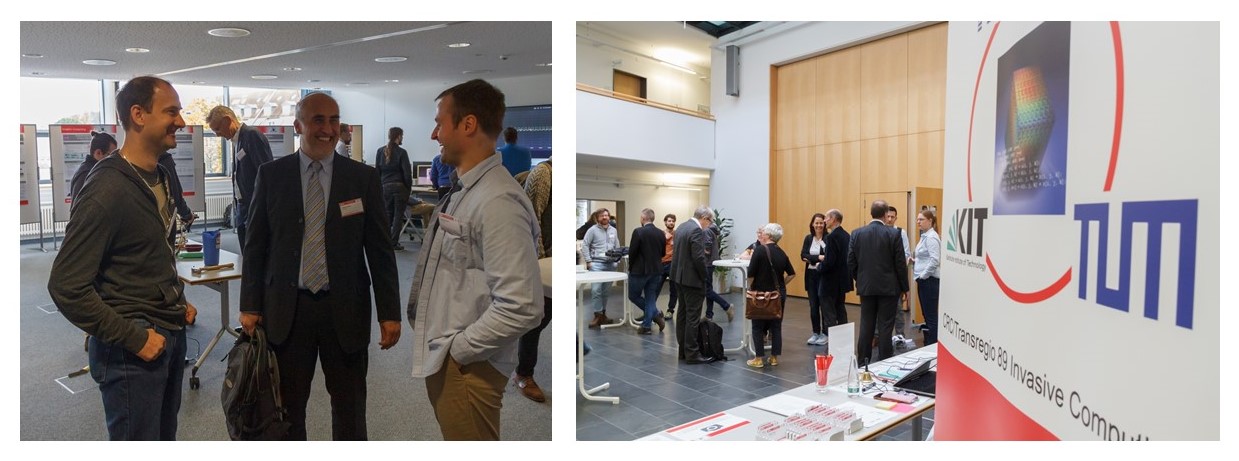

More than twelve years of collaborative research on Invasive Computing found a celebratory ending at the Fraunhofer IIS, where it all began. On this occasion, researchers, reviewers, experts and alumni met for the InvasIC Colloquium.

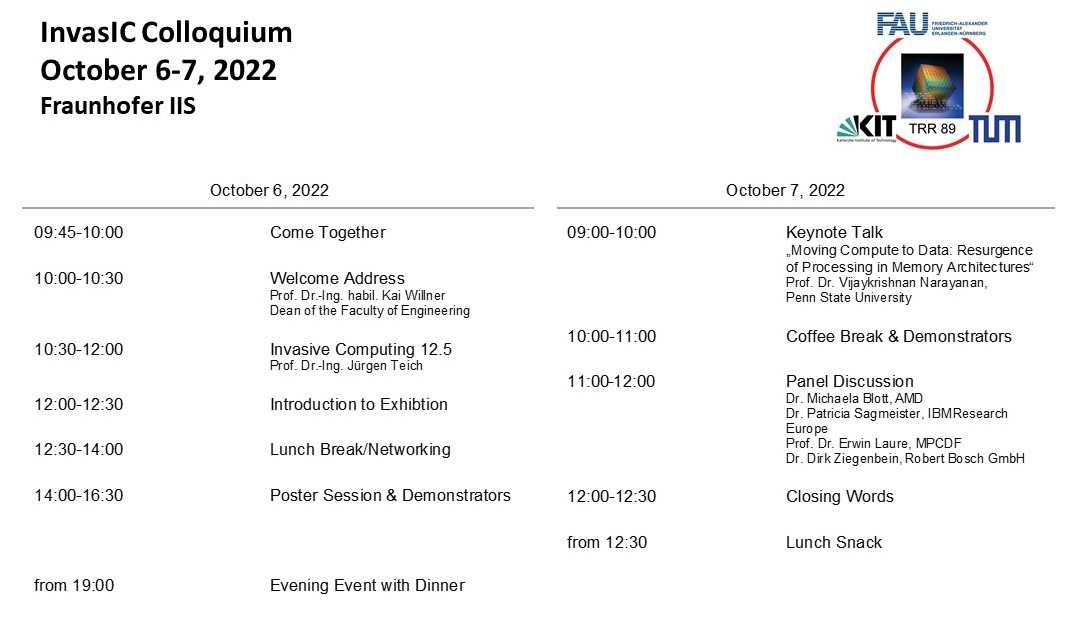

Agenda of the InvasIC Colloquium

Professor Teich opened the InvasIC Colloquium and welcomed the guests. He then gave an overview talk of the last 12.5 years of collaborative research in the field of Invasive Computing.

Prof. Teich opened the InvasIC Colloquium

After that, the guests had the opportunity to network and to visit the exhibition of the subprojects and Global Demonstrators. Each subproject presented its research with a scientific poster. The highlight of the exhibiton were the four Global Demonstrators, which made the research visible for everyone.

Global Demonstrators

Come together at the InvasIC Colloquium

The day finally came to a festive ending at the evening event with an italian dinner, musical performances and presentations from selected alumni.

Evening event with dinner and entertainment

On the second day of the InvasIC Colloquium, Prof. Dr. Vijaykrishnan Narayanan from Penn State University gave a Keynote Talk about "Moving Compute to Data: Resurgence of Processing in Memory Architectures". After that, four experts of the industry board took a stand on the question of „How relevant are many-core architectures, and in particular their compliance to non-functional requirements, in your own professional area?”

Keynote Talk of Prof. Dr. Vijaykrishnan Narayanan

Invasive Computing at the Hannover Messe

May 30 - June 2, 2022

Christian Heidorn and Torsten Klie at Hannover Messe 2022

Our Transregional Collaborative Research Center Invasive Computing showed together with the FAU Research Center Embedded Systems Initiative (FAU ESI) a demonstrator for hand sign recognition via Deep Learning on tightly-coupled processor arrays (TCPAs) as part of the BayernInnovativ joint booth at the Hannover Messe 2022. The interest in the "Future Hub" in Hall 2 was unbroken and the traffic at the booth was comparable to previous years.

Events 2021

58th Design Automation Conference (DAC'21), San Francisco, USA, December 5-9, 2021:

Prof. Dr.-Ing. Jörg Henkel (Chair for Embedded Systems, KIT)

Prof. Dr.-Ing. Jörg Henkel was the Conference Program Chair of the 58th Design Automation Conference (DAC'21). more information

Scopus data bank: Rank 30 and 39 in Hardware & Architecture, November 9, 2021:

Prof. Dr.-Ing. Jörg Henkel (KIT) & Prof. Dr.-Ing. Jürgen Teich (FAU)

According to new evaluation of the Scopus data bank done by the Stanford University, Prof. Dr.-Ing. Jörg Henkel ranks on place 30 and Prof. Dr.-Ing. Jürgen Teich ranks on place 39 of the most cited scientists in the science field of hardware and architecture. Congratulations! more information

ICCAD 2021 hosting 6th Workshop on Approximate Computing, November 4, 2021

Prof. Dr.-Ing. Jürgen Teich (FAU)

Together with Alexandra Kourfali, University of Stuttgart, Alberto Bosio, Ecole Centrale de Lyon, and Alessandro Savino, Politecnico di Torino, Jürgen Teich was chairing the 6th Workshop on Approximate. The virtual event was co-located this year with ICCAD 2021.

Dagstuhl Seminar 21441 (former 20291) "Adaptive Resource management for HPC Systems", Schloss Dagstuhl, November 1-5, 2021:

Prof. Dr. Michael Gerndt (TUM), Masaaki Kondo (University of Tokyo, Japan), Barton P. Miller (University of Wisconsin, USA) and Tapasya Patki (LLNL, USA)

Participants of the Dagstuhl Seminar 21441, November 1-5, 2021.

This Dagstuhl Seminar investigated a holistic, layered approach for adaptive resource management. It started with the resource management layer being responsible for scheduling applications on the machine and dynamically allocating resources to the running applications. At the programming level, applications need to be programmed in a resource-aware style such that they can adapt to resource changes and can make most efficient usage of the resources. On top of the programming interfaces, programming tools have to be available that allow the application developers to analyze and tune the applications for the varying amount of available resources. At the application level, applications have to be redesigned to enable significant gains in efficiency and throughput, e.g., adaptive mesh refinement, approximate computing, and power-aware algorithms are a few aspects to mention here. The outcomes of this seminar were a list of challenges and a roadmap that identified the next steps for implementing adaptive resource management of HPC systems including languages, message passing libraries, resource managers, tools, and runtimes. more information

HiPEAC Computing Week, Lyon, October 25, 2021:

Opening Keynote: Enforcement of Non-functional Program Requirements on MPSoCs

Prof. Dr.-Ing. Jürgen Teich (FAU) Hosted by the University of Lyon, this Computing Systems Week brings the HiPEAC community together with the *systems-on-chip and embedded systems/connected objects research group at CNRS*, see here for details

Prof. Dr.-Ing. Jürgen Teich (FAU) giving the opening keynote speech at the HiPEAC Computing Week.

Many embedded applications require non-functional requirements such as safety, reliability, and execution time to be guaranteed during the execution of respective programs on modern Multi-Processor System-on-Chip (MPSoC) platforms. Unfortunately, current compilers and operating systems are not aware of such requirements and thus no able to satisfy, or even counter-productive in satisfying these, e.g., by sharing resources unnecessarily between application programs and thus creating execution interference.

In this talk, we first introduce the concept and principles of Invasive Computing that allows a programmer to claim a set of resources exclusively, e.g., CPU cores, for each application. Importantly, this not only creates an on-demand isolation of elsewise interfering programs, but as a result allows to then apply static analysis and optimization techniques to optimize the deployment of applications on a given MPSoC. Unfortunately, jitter and variability of non-functional program execution qualities such as, e.g., latency or throughput may still remain to a certain degree due do either exogeneous noise influences such as data-dependent input workload, but also induced currently by MPSoC-internal system management software, e.g., dynamic power management. As a remedy, we presented novel techniques named Run-time Requirement Enforcement (RRE) to support the satisfaction of given non-functional execution requirements for individual applications in tight bounds at run-time. These are based on Enforcement Automata. These sense the incoming workload variation at run-time while adjusting core and power management in reaction. It was shown that these can be generated and even formally verified statically prior to their deployment for run-time control of a given set of requirements. For image and other types of streaming applications, we provided intuitive examples that by controlling DVFS settings of invaded CPU cores either pro-actively or re-actively, not only tight execution times, but also power corridors may be strictly enforced, or alternatively the number of violations or return times to satisfaction of requirements minimized.

G'SCHEID SCHLAU!, October 23, 2021:

Franziska Schirrmacher (FAU)

Franziska Schirrmacher took part in a discussion on AI together with the Minister of Science Bernd Sibler and Professor Markus Kaiser from TH Nürnberg. The event was part of the series "Siblers DenkRäume" where Bernd Sibler engages in conversations with citizens about current socially relevant topics such as artificial intelligence (AI). The discussion revolved around the topic "KI... und ich? Von der Bilderkennung bis zu Social Media. KI in unseren Medien". It was on the agenda of "G'SCHEID SCHLAU !" and took place at the Deutsches Museum Nürnberg. As a doctoral researcher, Franziska is currently developing AI methods for side channel detection in the TRR 89. To find out more, you can watch the video of the discussion here.

Institut des nanotechnologies de Lyon (INL), September 14, 2021:

Invited Talk: Enforcement of Non-functional Program Requirements on MPSoCs

Prof. Dr.-Ing. Jürgen Teich (FAU)

Many embedded applications require non-functional requirements such as safety, reliability, and execution time to be guaranteed during the execution of respective programs on modern Multi-Processor System-on-Chip (MPSoC) platforms. Unfortunately, current compilers and operating systems are not aware of such requirements and thus no able to satisfy, or even counter-productive in satisfying these, e.g., by sharing resources unnecessarily between application programs and thus creating execution interference.

In this talk, we first introduced the concept and principles of Invasive Computing that allows a programmer to claim a set of resources exclusively, e.g., CPU cores, for each application. Importantly, this not only creates an on-demand isolation of elsewise interfering programs, but as a result allows to then apply static analysis and optimization techniques to optimize the deployment of applications on a given MPSoC. Unfortunately, jitter and variability of non-functional program execution qualities such as, e.g., latency or throughput may still remain to a certain degree due do either exogeneous noise influences such as data-dependent input workload, but also induced currently by MPSoC-internal system management software, e.g., dynamic power management. As a remedy, we presented novel techniques named Run-time Requirement Enforcement (RRE) to support the satisfaction of given non-functional execution requirements for individual applications in tight bounds at run-time. These are based on Enforcement Automata. These sense the incoming workload variation at run-time while adjusting core and power management in reaction. It was shown that these can be generated and even formally verified statically prior to their deployment for run-time control of a given set of requirements. For image and other types of streaming applications, we provided intuitive examples that by controlling DVFS settings of invaded CPU cores either pro-actively or re-actively, not only tight execution times, but also power corridors may be strictly enforced, or alternatively the number of violations or return times to satisfaction of requirements minimized.

NUERNBERG DIGITAL 2021: Digital Gender Gap

Dr. Sandra Mattauch and Franziska Schirrmacher (FAU)

Once a year, the Nuremberg Digital Festival connects people in the Nuremberg metropolitan region for ten days on the central topics of digitization in business, science, education and culture. The festival sees itself as an open participatory format for the digital community: regional organizations take part as organizers to exchange knowledge and discuss the opportunities and risks of the digital society. In the realm of the Nuremberg Digital Festival Sandra Mattauch and Franziska Schirrmacher from our Transregio, were interviewed regarding the topic “The Gender Gap” in informatics. See the full article on page 22. NUERNBERG DIGITAL 2021: Digital Gender Gap

Nomination for KI-Newcomer 2021

Franziska Schirrmacher (FAU)

Franziska was nominated for KI-Newcomer 2021. As a doctoral researcher she is currently developing AI methods for side channel detection in the TRR 89. To find out more, read Franziskas interview with FAU aktuell here.

Member of the German Society of Humboldtians, Virtual Event, February 18, 2021:

Prof. Dr.-Ing. Jürgen Teich (FAU)

The German Society of Humboldtians (www.dgh-ev.org) welcomes Jürgen Teich as a new member for his merits as a host of Humboldtians, reviewer for the Humboldt Foundation (AvH) and his numerous contacts to and stays at foreign universities.

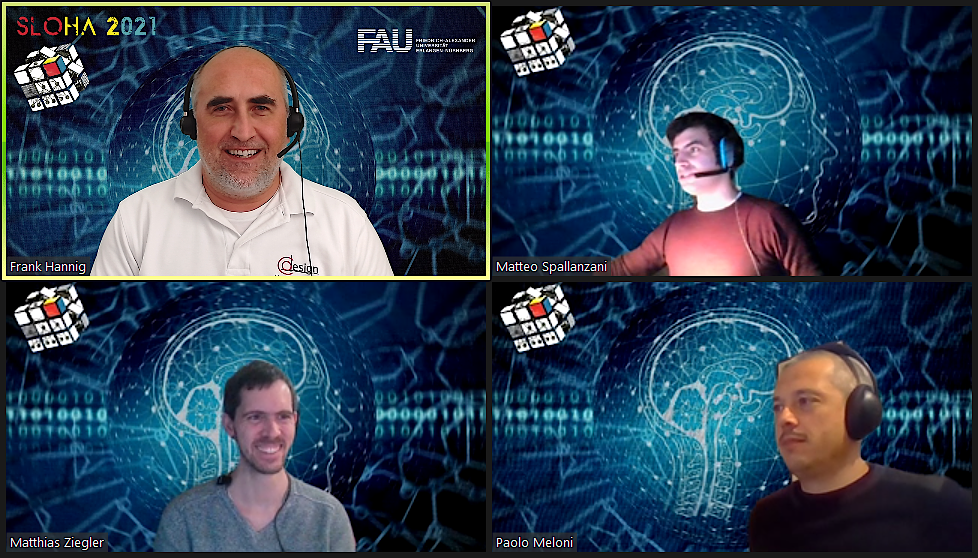

DATE Friday Workshop SLOHA 2021, Virtual Workshop, February 5, 2021:

Dr.-Ing. Frank Hannig (Hardware/Software Co-Design, FAU)

On February 5, 2021, the first "DATE Friday Workshop System-level Design Methods for Deep Learning on Heterogeneous Architectures (SLOHA 2021)" took place co-located with the Conference on Design, Automation and Test in Europe (DATE). The SLOHA Workshop, initiated and co-organized by Frank Hannig, addressed machine learning topics on heterogeneous computing architectures (e.g., dedicated accelerators, GPUs, FPGAs) and autonomous vehicles. The workshop program consisted of keynote talks (Luca Benini, ETH Zurich on "In-Sensor ML - Heterogeneous Computing in a mW" and Michaela Blott, Xilinx Research on "Specialization in Hardware Architectures for Deep Learning") and peer-reviewed submissions. Furthermore, results of the BMBF-funded project "KISS: AI Laboratory for System-level Design of ML-based Signal Processing Applications" (https://www.iis.fraunhofer.de/kiss)/ were presented. The substantial number of 76 registered participants reflected the very topics and attractiveness of the workshop program. More information is available on the SLOHA 2021 website: https://www12.cs.fau.de/ws/sloha2021/.

Organizing Committee of the DATE Friday Workshop SLOHA, February 5, 2021.

Siemens Master Prize, Virtual Event, February 5, 2021:

Armin Schuster (FAU)

Armin Schuster was honored on February 5, 2021 as part of the virtual graduation ceremony of the technical faculty. For his master's thesis "Design Space Exploration of Approximate CNN-Inference with Variable Precision", supervised by Professor Teich, from Siemens / Corporate Technology, he received the Siemens Master Prize in the Information and Communication Technology course.

Invasic Computing at HiPEAC Computer Systems Week 2021, Virtual Conference, January 20, 2021:

Invited Talk: A Comparative Evaluation of Latency-Aware Energy Optimization Approaches in Many-Core Systems

Prof. Dr.-Ing. Jürgen Teich (FAU)

Prof. Teich give an invited talk within the Workshop on Next Generation Real-Time Embedded Systems (NG-RES 2021) at HiPEAC Computer Systems Week 2021.

Events 2020

MLCAD 2020: 2nd ACM/IEEE Workshop on Machine Learning for CAD:

Prof. Dr.-Ing. Ulf Schlichtmann (Chair of Electronic Design Automation, TUM)

November 16-20, 2020: Prof. Dr.-Ing. Ulf Schlichtmann (TUM) served as General Chair of 2nd ACM/IEEE Workshop on Machine Learning for CAD (MLCAD 2020). Advances in machine learning (ML) over the past half-dozen years have revolutionized the effectiveness of ML for a variety of applications. However, design processes present challenges that require parallel advances in ML and CAD as compared to traditional ML applications such as image classification. As such, the purpose of the workshop is to discuss, define and provide a roadmap for the special needs for ML for CAD where CAD is broadly defined as design-time techniques as well as run-time techniques.

IEEE CEDA Presentation Library:

Jan Spieck, Dr.-Ing. Stefan Wildermann and Prof. Dr.-Ing. Jürgen Teich (Hardware/Software Co-Design, FAU)

November 11, 2020, The IEEE Council on Electronic Design Automation (CEDA) is a centralized resource for viewing videos and presentations from conferences, webinars, and lecturers. The video presentation "Scenario-Based Soft Real-Time Hybrid Application Mapping for MPSoCs" Prof. Teich held during the DAC conference 2020 was selected to be portrayed in this selective and well-frequented library website. View the presentation

The presentation "Scenario-Based Soft Real-Time Hybrid Application Mapping for MPSoCs" is now available in the IEEE CEDA presentation library.

IEEE Embedded Systems Week (ESWEEK 2020):

Prof. Dr.-Ing. Jürgen Teich (Hardware/Software Co-Design, FAU)

September 20-25, 2020, Prof. Teich is chairing the live Award Plenary Sessions at the Embedded Systems Week 2020. Due to the corona pandemic, the conference was held virtually this year. more information

Members of the Organizing Committee of the 16th ACM/IEEE Embedded Systems Week (ESWEEK 2020) during an Award Plenary session of the virtual conference.

AxC´20: 5th Workshop on Approximate Computing, San Francisco, USA:

Prof. Dr.-Ing. Jürgen Teich (Hardware/Software Co-Design, FAU)

July 19, 2020, San Francisco: Prof. Dr.-Ing. Jürgen Teich (FAU) served as Program Co-Chair of AxC´20: 5th Workshop on Approximate Computing, co-located with DAC 2020 in San Francisco. Nowadays, Approximate Computing (AxC) represents a novel and interesting design paradigm for building modern systems with better trade-off between efficiency, in terms of performance, power consumption, hardware area, execution timing, and the quality of the final outcomes. Indeed, AxC is based on the intuitive observation that, while performing exact computation requires a high amount of computational resources, allowing a selective approximation or an occasional relaxation of the specification may provide significant gains in energy efficiency. Suitable solutions will not be fully realized in a single layer only. Therefore, applying AxC in different layers of hardware, architecture, software and algorithms should be investigated. Moreover, while the hidden cost of AxC is a reduction of an application’s inherent resiliency to errors, AxC has also recently been demonstrated to be effective in safety-critical applications. This workshop (fifth edition after successful ones at Paderborn’15, ESWEEK’16, ETS’ 18, DATE’19) aimed at exploring AxC techniques applied at different layers, such as hardware, architecture, software and algorithms, making room for the exploration of methodologies able to exploit effective and real systems that can inspire application in many recent application domains such as machine learning, safety and security.

ACM/IEEE Early Career Workshop at DAC, San Francisco, USA:

Prof. Dr.-Ing. Jürgen Teich (Hardware/Software Co-Design, FAU)

July 19, 2020, San Francisco: Prof. Dr.-Ing. Jürgen Teich (FAU) was panelist at the ACM/IEEE Early Career Workshop. This workshop is for young and mid-career faculty and professionals in the fields related to electronic design automation (EDA). The workshop started in the morning with an interactive session borrowing techniques from IMPROV to help you improve your soft skills (interpersonal, communication etc.) with others. This was followed by presentations and panel discussions by professionals discussing diverse topics such as navigating the various challenges to better succeed and thrive in your academic or industry job, getting your projects funded and climbing academic and technical ladders, as well as improved cooperation between industry and academia research and development. In addition, the workshop provided rich opportunities to closely interact and network with some of the established academicians, professionals, and funding officers in EDA related fields. more information

Prof. Dr.-Ing. Jürgen Teich (FAU) was panelist at the ACM/IEEE Early Career Workshop 2020.

57th Design Automation Conference (DAC'20), San Francisco, USA:

Prof. Dr.-Ing. Jörg Henkel (Chair for Embedded Systems, KIT)

Prof. Dr.-Ing. Jörg Henkel was the Technical Program Chair of the 57th Design Automation Conference (DAC'20). DAC received a record number of 984 submissions out of which 228 were selected for the technical program. For the first time DAC was held as a virtual event with a mixture of pre-recorded and live content. more information

Prof. Dr.-Ing. Jörg Henkel was the Technical Program Chair of DAC'20.

The 31st IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP 2020), The University of Manchester, July 6-8, 2020:

Dr.-Ing. Frank Hannig (Hardware/Software Co-Design, FAU)

The 31st IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP 2020) was hosted by The University of Manchester, from July 6 to 7, 2020. ASAP 2020 took place as an Online Conference and attracted 110 participants. The conference continued the long-standing ASAP tradition of reporting top-notch results in application-specific computer architectures and related areas. In the welcome address, General Chair Dirk Koch (University of Manchester) and Program Co-Chair Dr.-Ing. Frank Hannig (FAU) highlighted the privilege of organizing ASAP and provided statistics on the submissions. In response to the call for papers, 118 abstract submissions with affiliations to 26 countries were received, and 87 papers went to the review process. With the help of 61 members of the Technical Program Committee, who carried out 340 reviews (about four per submission) and having intensely scrutinized the reviews, the organizers were pleased to present a high-quality technical program. The program included 21 long papers (24% acceptance rate) and 12 short papers at the online conference. The selected papers have been divided into thematic areas (six sessions), highlighting the current research endeavors within application-specific systems, architectures, and processors. The sessions covered topics on heterogeneous computing, reconfigurable accelerators, machine learning and acceleration of neural networks, cloud computing, emerging technologies, neuromorphic computing, edge computing, approximate computing, and computer arithmetic. The strong technical program was complemented by two keynote talks on: “An Overview of High Performance Computing and Using Mixed Precision in Numerical Computations to Speedup Linear Algebra Solvers” by Jack Dongarra, University of Tennessee and Oak Ridge National Laboratory, USA; and “Formally Verifying Hardware for Secure and Private Computing” by Satnam Singh, Google Research, USA.

Program Co-Chair Dr.-Ing. Frank Hannig (left). Socializing at the "After-ASAP Drink" (right).

Since networking and social aspects are often neglected at online conferences, there was an “After-ASAP Drink” at the end of the event. Here, everybody had his or her favorite drink ready for a video toast and online chat.

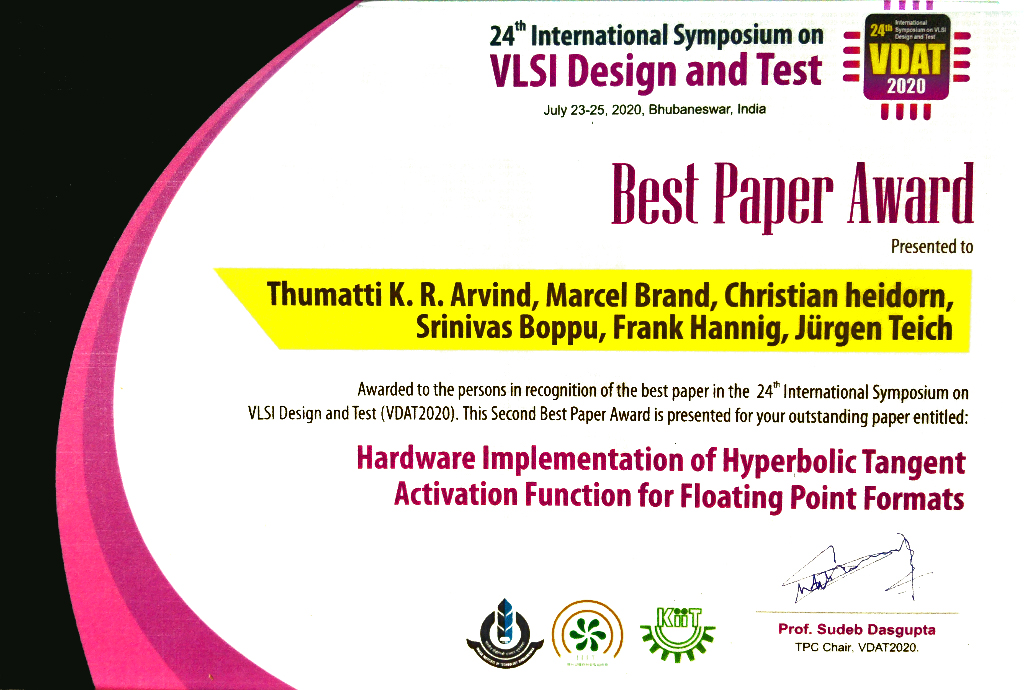

Best Paper Award at VDAT 2020, Bhubaneswar, India, July 2-4, 2020

T.K.R. Arvind, Marcel Brand, Christian Heidorn, Srinivas Boppu, Dr.-Ing. Frank Hannig and Prof. Dr.-Ing. Jürgen Teich

The paper "Hardware Implementation of Hyperbolic Tangent Activation Function for Floating Point Formats" presented at the 24th International Symposium on VLSI Design and Test (VDAT 2020) in Bhubaneswar, India won the Best Paper Award.

8th ACM Workshop on Information Hiding and Multimedia Security, June 22-25, 2020:

Franziska Schirrmacher (FAU)

Franziska Schirrmacher and Christian Riess (FAU) served as General Chairs of the ACM Workshop on Information Hiding and Multimedia Security. The workshop is well known in the multimedia security community and covers information hiding topics, such as watermarking, steganography, steganalysis, and covert channels. Multimedia identification and biometrics, just to name a few of the multimedia security topics, are also addressed in the workshop. The event was held as a virtual conference with a mixture of pre-recorded and live content.

Participants of the virtual ACM Workshop on Information Hiding and Multimedia Security 2020.

Detecting the Gender Gap in Computer Science — A Bibliometric Approach, May, 2020:

Dr. Sandra Mattauch (FAU), Dr. Katja Lohmann (Leibniz Universität Hannover), Dr.-Ing. Frank Hannig (FAU), Prof. Dr.-Ing. Daniel Lohmann (Leibniz Universität Hannover) and Prof. Dr.-Ing. Jürgen Teich (FAU)

Our manuscript entitled "Detecting the Gender Gap in Computer Science — A Bibliometric Approach" is published in Communications of the ACM.

The low share of women in computer science is documented by many surveys. Most of these studies are based on registrations or enrolments of universities or other scientific institutions. In this paper, we present an approach to a) detect the gender gap in the group of scientists that are currently active in research and b) classify differences for different fields of computer science. This group comprises professors, industrial researchers, senior lecturers, postdoctoral researchers, and doctoral students shortly before finishing their theses. The proportion of women in a specific scientific area of computer science might provide valuable information for strategies to recruit women as postdocs or professors.

Read the paper. Press release FAU

Dr. Sandra Mattauch and Dr. Katja Lohmann were interviewed about their study on Detecting the Gender Gap in Computer Science — A Bibliometric Approach.

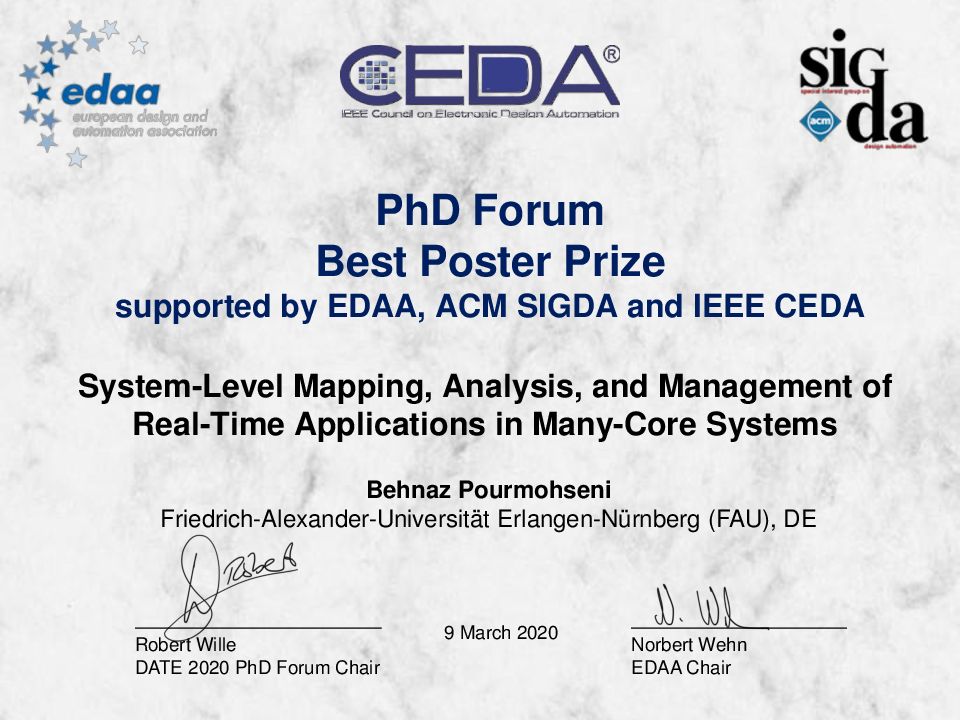

PhD Forum Best Poster Prize at DATE 2020, March 9, 2020:

Behnaz Pourmohseni (Hardware/Software Co-Design, FAU)

Behnaz Pourmohseni received the PhD Forum Best Poster Prize at DATE 2020 for her poster titled "System-Level Mapping, Analysis, and Management of Real-Time Applications in Many-Core Systems". The prize is supported by EDAA, ACM Sigda and IEEE CEDA. Due to the Covid-19 pandemic the DATE conference was held virtually.

Behnaz Pourmohseni receiving the PhD Forum Best Poster Prize at DATE 2020.

Dagstuhl Seminar 20081 "Scheduling", Schloss Dagstuhl, February 16-21, 2020:

Prof. Dr. Nicole Megow (UB), David Shmoys (Cornell University, USA) and Ola Svensson (EPFL, Switzerland)

Scheduling is a major research field that is studied from a practical and theoretical perspective in computer science, mathematical optimization, and operations research. Applications range from traditional production scheduling and project planning to the newly arising resource management tasks in the advent of internet technology and shared resources. Despite the remarkable progress on algorithmic theory for fundamental scheduling problems, new questions gain greater prominence due to the rise of new applications.

Participants of the Dagstuhl Seminar 20081 "Scheduling" February 16-21, 2020.

This Dagstuhl Seminar focused on the interplay between scheduling problems and problems that arise in the management of transportation and traffic. There are several notable aspects of the scheduling problems that arise particularly in this context: 1. the role of dynamic decision-making in which data-driven approaches emerge (especially those that have stochastic elements in modeling the multi-stage decision-making); 2. the interplay between scheduling aspects and what might be viewed as routing aspects, providing a spacial component to the nature of the scheduling problem; 3. the tension between questions of coordination and competition that arise from the fact that for many of the issues in this domain, there are significant questions that depend on the extent to which the traffic can be centrally coordinated. Since the community working on the intersection of scheduling and traffic is itself rather broad, we methodologically focus on the theoretical design of algorithms, mathematical optimization methods, and the interplay between optimization and game-theoretic approaches.

Invasic Computing at HiPEAC Computer Systems Week 2020, Bologna, January 21, 2020:

Invited Talk, HiPEAC Computer Systems Week 2020: Tackling the MPSoC Data Locality Challenge for Distributed-Shared Memory Architectures

Prof. Dr. Andreas Herkersdorf (Chair of Integrated Systems, TUM)

Prof. Herkersdorf gave an invited talk within the PARMA-DITAM: Workshop on Parallel Programming and Run-Time Management Techniques for Many-core Architectures / Workshop on Design Tools and Architectures for Multi-Core Embedded Computing Platforms at HiPEAC Computer Systems Week 2020.

Data access latencies and bandwidth bottlenecks frequently represent major limiting factors for the computational effectiveness of multi- and many-core processor architectures. This talk introduces two conceptually complementary approaches to reduce the synchronization overheads for coherence maintenance and to improve the locality between computing resources and data: Region-based cache coherence and near memory acceleration. The presented approaches represent current work in the DFG Transregional Collaborative Research Center “Invasive Computing”. A 2D array of compute tiles with multiple, heterogeneous RISC cores, two levels of caches and a tile-local SRAM memory serves as reference processing platform. Compute tiles, I/O tiles and globally shared DDR SDRAM memory tiles are interconnected by a meshed Network on Chip (NoC) with support form multiple quality of service levels. Overall, this processing architecture follows a distributed-shared-memory model. The limited degree of parallelism in many embedded computing applications also bounds the number of compute tiles possibly sharing associated data structures. Therefore, we envision region-based cache coherence (RBCC) among a limited working set of compute tiles over global coherence approaches. Coherence regions can dynamically be reconfigured at run time and comprise a number of arbitrary (adjacent or non-adjacent) compute tiles which are interconnected through regular NoC channels for the exchange of coherency protocol messages. We will show that region-based coherence allows maintaining substantially smaller coherence directories(e.g., by approx. 40% reduced in size for 16 tiles systems with up to 4 tiles per region) and shorter sharer checking latencies than global coherence. Near memory processing is an alternative concept to increase data/task locality by means of near memory accelerators (NMA). NMA positions processing resources for specific forms of data manipulations as close as possible to the data memory. The evident benefits are: reducing global interconnect usage,shortening of access latencies and, thus, increasing compute efficiency. In distributed-shared-memory architectures, where accelerator units can be affiliated with different tile-local SRAMs as well as with the globally shared DDRSDRAM, near memory acceleration requires thorough consideration of task mapping as well as task and data migration into and among compute tiles.

Invited Talk, HiPEAC Computer Systems Week: Secure hardware composition: starting from the root of trust

Prof. Dr. Ingrid Verbauwhede (KU Leuven, BE)

Prof. Verbauwhede gave an invited talk within the PSeHAS: Workshop on Secure Hardware, Architectures, and Operating Systems at HiPEAC Computer Systems Week 2020. What is “hardware” security? The network designer relies on the security of the router box. The software developer relies on the TPM (Trusted Platform Module). A system designer assume that cryptographic keys, random initial values, nonces, freshness, hardware isolation, or secure storage is available. At the same time, electronics shrink: sensor nodes, IOT devics, smart devices are becoming more and more available. Adding security and cryptography to these often very resource constraint devices is a challenge. This presentation will focus on how to create secure platforms from the bottom-up, starting from the roots of trust.

At the HiPEAC Computer Systems Week Prof. Verbauwhede was also invited to give an interview. She sets out why hardware needs to be secure by design, with some alarming examples of what can happen if security is poorly implemented. She explains why there should be more guarantees of security in products and why Europe should build on its leading position in this field.

Workshop on the Computing Continuum at HiPEAC Computer Systems Week 2020:

Prof. Dr. Michael Gerndt, Prof. Dr.-Ing. Walter Stechele (TUM) and Sven Karlsson (Ericsson)

Computing Continuum Workshop at HiPEAC (photographs HiPEAC 2020).

The HiPEAC Computer Systems Week took place in Bologna, Italy on January 20, 2020. The face of computing has changed dramatically in recent years. A large variety of devices such as simple sensors and microcontrollers, edge computers, mobile devices, laptops, servers, clusters, and HPC systems build a ubiquitous infrastructure, called the Computing Continuum. Many of today’s applications from areas such as industrial production (Industry 4.0), social networks, precision medicine and large scientific experiments require a dynamically varying amount of compute and storage capacity for gathering and processing large data sets to form the basis for advanced services. The need for dynamics is due to changes in the data rates, the services request rates, as well as the delivery process. The resources of the continuum are typically shared among different tenants and applications. Sharing resources is, for example, the driving force in today’s cloud offerings and their extensions into distributed infrastructures in the form of edge and fog computing as well as the mobile extensions based on radio networks. Efficient sharing requires dynamic and data- and application-aware scheduling of tasks onto the available resources. Further, careful resource management and resource isolation is used to enable performance guarantees. This is especially important in HPC and embedded computing. Sharing reduces over-provisioning but requires careful dynamic management of shared resources, including on-chip communication, memory hierarchy, and power.

This workshop had the goal to gather application scenarios as well as resource management technologies for the Computing Continuum. Topics to be covered included:

- Distributed scientific, social, web, IoT, and enterprise applications

- Application architecture models such as workflows, microservices, function-as-a-service, and cloud native applications, streaming applications

- Concepts for resource aware programming

- Application characterization and performance modeling

- Dynamic application tuning for performance and energy

- Smart orchestration and self-adaptive resource provisioning

- Horizontal and vertical auto-scaling across cloud and edge

- Operating system concepts such as uni-kernel

- Computer systems and computer architectures for the compute continuum

- Communication models

Talks from Young Scientists and Doctoral Researchers at HiPEAC Computer Systems Week 2020:

Dr. Bertrand Simon (UB), Jophin John (TUM), Florian Schmaus and Behnaz Pourmohseni (FAU)

Dr. Bertrand Simon (left) and Behnaz Pourmohseni (right) at HiPEAC.

At HiPEAC Computer Systems Week 2020 our young scientists gave talks on their current work. Florian Schmaus talked about "Towards Taming the Computing Continuum: System Software for Future Many-Core Architectures" and Dr. Bertrand Simon about "Energy Minimization in DAG Scheduling on MPSoCs at Run-Time: Theory and Practice". Behnaz Pourmohseni presented her work on "Real-Time Task Migration for Dynamic Resource Management in Many-Core Systems". Jophin John gave a talk on "Dynamic Resource Management on HPC Systems to enable integration into the Computing Continuum."

Events 2019

VDE Award 2019, Munich, November 24, 2019

Nael Fasfous (Integrated Systems, TUM)

Nael Fasfous from TUM has been awarded the VDE Award 2019, in recognition of his Master Thesis on the topic of "Compact Directories with Hybrid Architecture Aware Eviction Policies for Distributed Shared Memory MPSoCs". In his thesis, Nael proposed innovative cache eviction strategies for Multiprocessor System-on-Chip architectures. Within Project B5, Akshay Srivatsa was the advisor of this thesis. The VDE Award has been given to Nael Fasfous from the Association of German Engineers (Verein Deutscher Ingenieure, VDE Südbayern) on November 24, 2019. more information

Nael Fasfous (Integrated Systems, TUM) has been awarded the VDE Award 2019.

Keynote Talk, 26th ACM Conference on Computer and Communications Security in London, UK, November 11-15, 2019: The Need for Hardware Roots of Trust

Prof. Dr. Ingrid Verbauwhede (KU Leuven, BE)

Prof. Verbauwhede (KU Leuven, BE) gave a talk on "The Need for Hardware Roots of Trust" at the 26th ACM Conference on Computer and Communications Security in London.

Electronics are shrinking and penetrating all aspects of our lives. IOT devices fill our homes, cars are driving autonomously, body area networks monitor our health. Adding security and cryptography to these often very resource constraint devices is a challenge. We would like the solutions to be lightweight and at the same time resistant to remote as well as local physical manipulation attacks.Software and cryptographic security protocols rely on hardware roots of trust. Protocol designers assume that cryptographic keys, random initial values, nonces, freshness, hardware isolation, or secure storage is simply available to them. This presentation focused design methods for hardware roots of trust in general and more specifically on Physically Unclonable Functions (PUFs) and True Random Number Generators (TRNG), two essential roots of trust.

Invited Talk, Kolkom 2019, University of Paderborn, November 7-9, 2019: A Combinatorial optimization with explorable uncertainty

Prof. Dr. Nicole Megow (UB)

Prof. Megow gave an invited talk on "A Combinatorial optimization with explorable uncertainty" at the Colloquium on Combinatorics (Kolkom 2019) at University of Paderborn.

In the traditional frameworks for optimization under uncertainty, an algorithm has to accept the in-completeness of input data. Clearly, more information or even knowing the exact data would allow for significantly improved solutions. How much more information suffices for obtaining a certain solution quality? Which information shall be retrieved? Explorable uncertainty is a recently proposed framework in which parts of the input data are initially unknown, but can be obtained at a certain cost using queries. An algorithm can make queries one by one until it has obtained sufficient information to solve a given problem. The challenge lies in balancing the cost for querying and the impact on the solution quality. In this talk, we give a short overview on recent work on explorable uncertainty for combinatorial optimization problems, focussing on the minimum spanning tree problem and a scheduling problem.

Kolkom 2019 - Invited speakers and organizers.

Kolkom 2019 - Invited speakers and organizers.

LZE Tech Day, Erlangen, November 7, 2019:

The Leistungszentrum Elektroniksysteme (LZE) is a joint initiative of the Fraunhofer-Gesellschaft, its Institutes IIS and IISB and the Friedrich-Alexander-University Erlangen-Nürnberg (FAU), together with other non-university research institutions and associated industrial partners. The LZE is breaking new ground here. With novel structures and cooperation models between science and industry, the successful transfer of research results has been initiated.

Impressions from the LZE Tech Day 2019.

At the LZE Tech Day, examples from different stages of the innovation chain were shown ranging from new wide-range wireless communication technology as a best practice for comprehensive, successful market development, to completed research projects that are in the early stages of exploitation, to technological development that is just beginning. We presented an invasive parallel Shallow Water application demonstration to raise awareness for the research work of the Transregio 89.

Keynote Talk, NorCAS 2019, Helsinki, October 29, 2019: Tackling the MPSoC Data Locality Challenge with Regional Coherence and Near Memory Acceleration

Prof. Dr. Andreas Herkersdorf (Chair of Integrated Systems, TUM)

Prof. Dr. Andreas Herkersdorf presented major results of our work done within project B5 at the IEEE Nordic Circuits and Systems Conference (NorCAS) 2019 in Helsinki. Data access latencies and bandwidth bottlenecks frequently represent major limiting factors for the computational effectiveness of multi- and many-core processor architectures. This keynote talk introduced two conceptually complementary approaches to reduce the synchronization overheads for coherence maintenance and to improve the locality between computing resources and data: Region-based cache coherence and near memory acceleration.

A 2D array of compute tiles with multiple, heterogeneous RISC cores, two levels of caches and a tile-local SRAM memory serves as reference processing platform. Compute tiles, I/O tiles and globally shared DDR SDRAM memory tiles are interconnected by a meshed Network on Chip (NoC) with support for multiple quality of service levels. Overall, this processing architecture follows a distributed-shared-memory model. The limited degree of parallelism in many embedded computing applications also bounds the number of compute tiles possibly sharing associated data structures. Therefore, we envision region-based cache coherence (RBCC) among a limited working set of compute tiles over global coherence approaches. Coherence regions can dynamically be reconfigured at runtime and comprise a number of arbitrary (adjacent or non-adjacent) compute tiles which are interconnected through regular NoC channels for the exchange of coherency protocol messages. We showed that region-based coherence allows maintaining substantially smaller coherence directories (e.g., by approx. 40% reduced in size for 16 tiles systems with up to 4 tiles per region) and shorter sharer checking latencies than global coherence.

Near memory processing is an alternative concept to increase data/task locality by means of near memory accelerators (NMA). NMA positions processing resources for specific forms of data manipulations as close as possible to the data memory. The evident benefits are: reducing global interconnect usage, shortening of access latencies and, thus, increasing compute efficiency. In distributed-shared-memory architectures, where accelerator units can be affiliated with different tile-local SRAMs as well as with the globally shared DDR SDRAM, near memory acceleration requires thorough consideration of task mapping as well as task and data migration into and among compute tiles.

Invited Talk, AI College of National Chiao Tung University in Tainan, Taiwan, October 23, 2019: Novel Ideas in Timing of Digital Circuits

Prof. Dr.-Ing. Ulf Schlichtmann (Chair of Electronic Design Automation, TUM)

Prof. Dr.-Ing. Ulf Schlichtmann visited Prof. Mark Po-Hung Lin at the AI College of National Chiao Tung University in Tainan, Taiwan. He gave a talk on "Novel Ideas in Timing of Digital Circuits" which included signficant research contents on Invasive Computing. Prof. Lin’s students engaged in discussion and gave creative suggestions. One researcher is so excited that she wants to visit TUM now.

The photo shows Ulf Schlichtmann with his host, Prof. Mark Po-Hung Lin, and his students together with another visitor.

The photo shows Ulf Schlichtmann with his host, Prof. Mark Po-Hung Lin, and his students together with another visitor.

Invasive Computing at the "Lange Nacht der Wissenschaften", Erlangen, October 19, 2019:

Every other year, the Long Night of the Sciences electrifies the metropolian region around Nuremberg, Fürth and Erlangen. This kind of event is the biggest in Germany with around 20,000 visitors. Researchers take this terrific possibility to showcase their research work to the broad audience. Also we took the chance to present the Transregio 89 (Invasive Computing).

Impressions from the Long Night of Sciences 2019 at FAU.

Impressions from the Long Night of Sciences 2019 at FAU.

On one hand, we demonstrated research on real-time multicore computing to visitors who are already familiar with Computer Science. In turn, the demonstrations opened up for interesting discussions about the characteristics of invasive computing. On the other hand, we introduced "InvasiTrax", a game based on the GraviTrax construction kit being very popular among children as a perfect way to explain invasive computing to people who have never heard of it before. Interactively visitors experience the differences between a "normal" multicore system and a system built upon invasive computing. InvasiTrax was particularly well received by children. We are very pleased that also a lot of girls came around to get to know InvasiTrax and learn something about invasive computing. Maybe we could contribute to more female students deciding for a STEM study program in the future. Moreover, our self-made movie "InvasIC for Dummies" (see https://www.youtube.com/watch?v=4kOQYHhnZW0) was shown, adding a touch of multimedia to our presentation. Furthermore, we portrayed general information about the Transregio at a poster. All in all, we are very satisfied with the Long Night of the Sciences 2019. We have been able to introduce invasive computing to a large number of visitors enlarging the comprehension for this young research field and raise awareness for Computer Science in general.

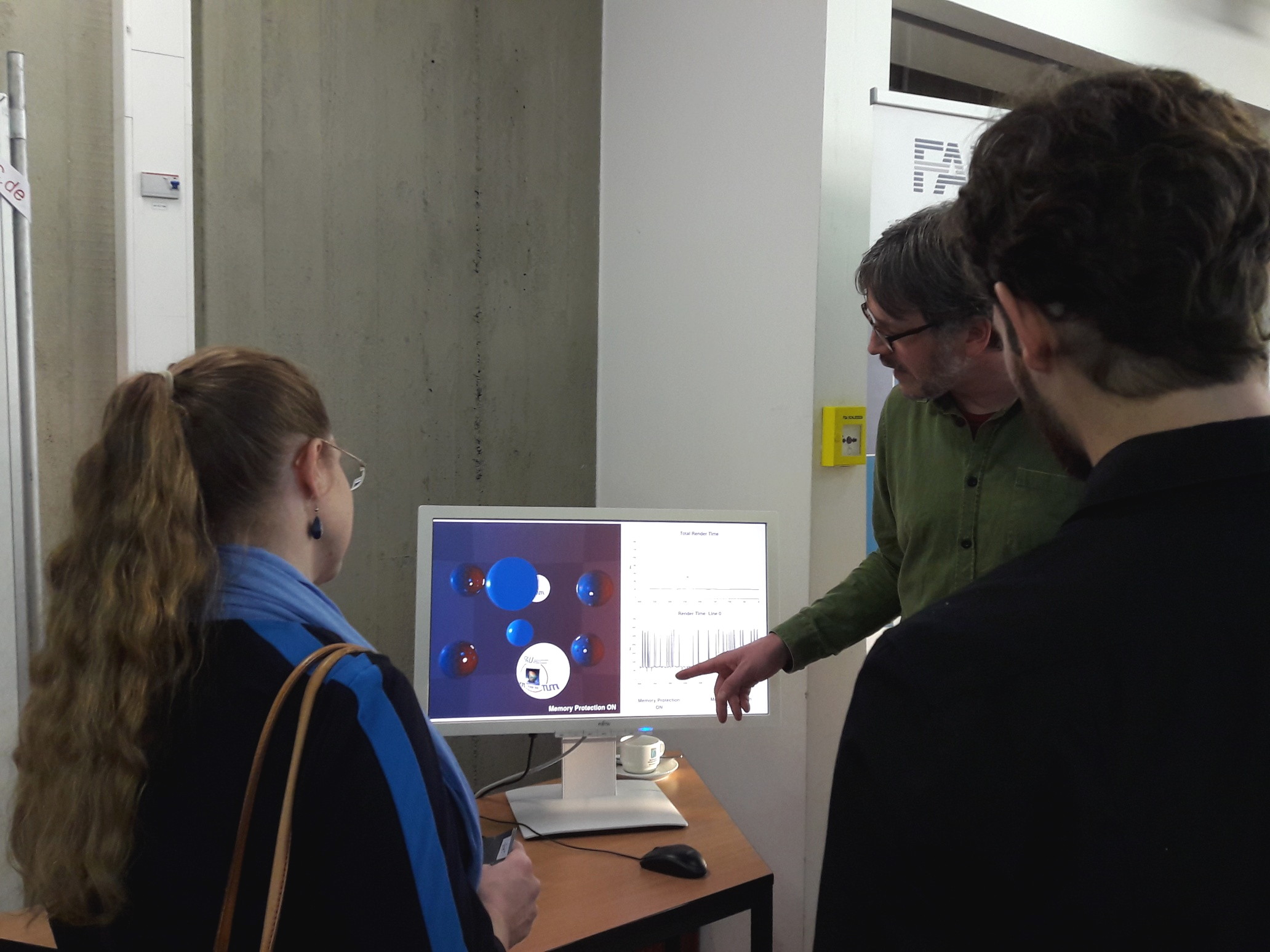

Invited Talk, University of Otago, October 4, 2019: Adaptive Memory Protection for Many-core Systems

Prof. Dr.-Ing. Wolfgang Schröder-Preikschat (Distributed Systems and Operating Systems, FAU)

Prof. Dr.-Ing. Wolfgang Schröder-Preikschat gave an invited talk at the University of Otago, New Zealand on "Adaptive Memory Protection for Many-core Systems".

Hardware-based memory protection is widely applied in all areas of computing, it is a fundamental building block for safety and security. However, improving protection measures by means of dedicated hardware such as a memory management unit (MMU) is not carved in stone, but rather depends on the application domain and the facts of the programming system and hardware, respectively. State of the art operating systems statically determine whether or not software entities are subject to memory protection. If enabled, costly operations will follow due to multi-level page-table handling, TLB (translation look-aside buffer) invalidations, and the release of inter-processor interrupts. This all reduces performance, increases operating-system noise, and makes system behavior unpredictable. If application programs are type-safe, then enabled hardware protection becomes a pretty much superfluous features. Contrariwise, if the programs are type-unsafe, disabled hardware protection opens door and gate for malware. This talk was on adaptive memory-protection that is capable of dynamically changing the per-program protection state. The feature is triggered at load/unload time of application programs and applies in the background of running processes. Measurement results were presented and discussed in terms of timing predictability of the system.

Invited Talk, University of Wellington, September 23, 2019: Predictability Issues in Operating Systems: Time, Space, Energy

Prof. Dr.-Ing. Wolfgang Schröder-Preikschat and Dr.-Ing. Timo Hönig (Distributed Systems and Operating Systems, FAU)

Prof. Dr.-Ing. Wolfgang Schröder-Preikschat and Dr.-Ing. Timo Hönig gave an invited talk at the Victoria University of Wellington, New Zealand on "Predictability Issues in Operating Systems: Time, Space, Energy".

Predictability is always subject to the underlying assumptions being made. For real-time systems, time response of processes in relation to the strictness of deadlines is of particular importance. With an additional focus on embedded systems, space and energy requirements become relevant as well and need to be considered in combination. As far as software is concerned, structure and organisation of the programs to be executed determines whether or not predictable processes will take place in a given computing system. Design for predictability is an overarching aspect that crosscuts the whole computing system and particularly addresses operating systems. This talk was about structuring principles of non-sequential programs - in the shape of but not limited to operating systems - to abet predetermination of quality attributes of non-sequential (real-time) processes, it was not about analytical methods to effectively predetermine these attributes. Issues in operating systems as to timing, space, and energy requirement were touched. Emphasis thereby was on coordination of cooperation and competition between processes, namely synchronisation. It was shown how measures of process synchronisation against the background of many-core processors cater to these issues.

Invited Talk, Workshop on Robust Optimiziation, University of Siegen, September 19-20, 2019: Optimization with Explorable Uncertainty

Prof. Dr. Nicole Megow (UB)

Prof. Megow gave an invited talk on "Optimization with Explorable Uncertainty" at the Workshop on Robust Optimiziation at the University of Siegen.

Explorable uncertainty refers to settings where parts of the input data are initially unknown, but can be obtained at a certain cost using queries. An algorithm can make queries one by one until it has obtained sufficient information to solve a given problem. The challenge lies in balancing the cost for querying and the impact on the solution quality. In this talk, we give a short overview on recent workon explorable uncertainty for combinatorial optimization problems, mention work on the minimumspanning tree problem, and then focus on a new scheduling problem.

Workshop on Robust Optimiziation, University of Siegen

Workshop on Robust Optimiziation, University of Siegen

New Zealand-Germany Research Workshop, University of Auckland, September 16, 2019:

Prof. Dr.-Ing. Wolfgang Schröder-Preikschat and Dr.-Ing. Timo Hönig (Distributed Systems and Operating Systems, FAU)

Prof. Dr.-Ing. Wolfgang Schröder-Preikschat and Dr.-Ing. Timo Hönig organised in cooperation with Prof. Dr. Zoran Salcic, Dr. Morteza Biglari-Abhari and Dr. Avinash Malik (UOA) a workshop on "Time predictability, energy awareness and security in embedded and real-time systems".

Penetration of embedded systems into all walks of our lives and domains of business activity, exemplified with the rise of Internet of Things, raises attention to many performance criteria for underlying systems and applications that are typically considered independent each of the other. Examples are timing predictability of execution, energy consumption awareness and security, to name a few. The workshop will centre on these issues and seek for synergies of research where more than one key performance parameters are targeted. System-level approaches and solutions were presented and discussed, as well as their implementations in real-world applications. The workshop included a number of invited participants and it was open for attendance to the other academic staff and research students from Department of Electrical, Computer and Software Engineering (ECSE) on first come first registered basis.

1st ACM/IEEE Workshop on Machine Learning for CAD (MLCAD), Canmore (Banff Area), September 3-4, 2019:

Prof. Dr.-Ing. Jörg Henkel (Chair for Embedded Systems, KIT) and Prof. Dr.-Ing. Ulf Schlichtmann (Chair of Electronic Design Automation, TUM)

This workshop focused on Machine Learning (ML) methods for all aspects of CAD and electronic system design. The predecessor of this workshop was held at the Design, Automation and Test in Europe (DATE) Conference in March 2019. The workshop was sponsored by both IEEE Council on Electronic Design Automation (CEDA) and ACM Special Interest Group on Design Automation (SIGDA). more information

Summer of Integration, August 7, TUM, 2019:

On the 7th of August researchers from different projects met for two days at TUM for their annual "Summer of Integration". This years meeting was dedicated to the joint improvement of the prototyping system and its infrastructure.

Invited Talk, International Symposium on Low Power Electronics and Design (ISLPED 2019), July 31, 2019: NCFET-Aware Voltage Scaling

Sami Salamin, Martin Rapp, Hussam Amrouch, Girish Pahwa, Yogesh Chauhan and Dr.-Ing. Jörg Henkel (Chair for Embedded Systems, KIT)

B2Run, Nuremberg, July 23, 2019: Run for Fun

"Run for Fun" was the theme under which our team participated at this year's B2Run in Nuremberg in July. The B2Run is a company racing series that is held at 17 locations in Germany. In Nuremberg the course leads around the great and the small Dutzendteich with the finish in the Max-Morlock-Stadium. Despite the very hot weather conditions all ten runners reached the finish of the almost 6 km long running track and enjoyed the great atmosphere. Inspired by the cheering spectators, the team proved that they can achieve a great deal together, whether on the PC, in the lab or in sports. Announcement on the FAU Homepage Announcement on Facebook

InvasIC-Runners at the B2Run 2019

Best Paper Award at SAMOS XIX Conference, Samos Island, Greece, July 11, 2019

Akshay Srivatsa, Sven Rheindt, Dirk Gabriel, Dr.-Ing. Thomas Wild and Prof. Dr. Andreas Herkersdorf (Chair of Integrated Systems, TUM)

The paper "CoD: Coherence-on-Demand – Runtime Adaptable Working Set Coherence for DSM-based Manycore Architectures" presented at this year's SAMOS Conference (International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation) received the best paper award.

In addition to this great success it is also worth noting that a second paper from the TRR 89 was a strong competitor and ended up on second position. "SHARQ: Software-Defined Hardware-Managed Queues for Tile-based Manycore Architectures" was written by Sven Rheindt, Sebastian Maier, Florian Schmaus, Dr.-Ing. Thomas Wild, Prof. Dr.-Ing. Wolfgang Schröder-Preikschat and Prof. Dr. Andreas Herkersdorf. The SAMOS Conference is annually taking place on the Samos Island, Greece. This years edition took place from July 7 to 11.

Invited Talks, Technische Universität Dortmund, July 4/5, 2019: Workshop on Embedded Systems, Dedicated to Peter Marwedel´s 70th Birthday

Prof. Dr.-Ing. Jürgen Teich (Hardware/Software Co-Design, FAU) and Prof. Dr. Andreas Herkersdorf (Chair of Integrated Systems, TUM)

Prof. Teich gave a talk about "Run-Time Enforcement of Non-functional Program Properties on MPSoCs". Prof. Herkersdorf talked about "As Embedded Systems Became Serious Grown-Ups, They Decide on Their Own". more information

Invited Talk, 9th International Workshop on Runtime and Operating Systems for Supercomputers (ROSS 2019), June 25, 2019: Asynchronous Abstract Machines: Anti-noise System Software for Many-core Processors

Sebastian Maier, Dr.-Ing. Timo Hönig, Peter Wägemann and Prof. Dr.-Ing. Wolfgang Schröder-Preikschat (Distributed Systems and Operating Systems, FAU)

Dr.-Ing. Timo Hönig held a talk on the paper "Asynchronous Abstract Machines: Anti-noise System Software for Many-core Processors".

Today's systems offer an increasing number of processor cores, however, the chance to operate them efficiently by dedicating cores to specific tasks is often missed. Instead, mixed workloads are processed by each core which leads to system noise (i.e., interferences, scheduling overheads) and yields subpar performance, only. We therefore propose a system design based on Asynchronous Abstract Machines (AAMs). An AAM features a light-weight scheduler and is dedicated to a specific group of tasks with common characteristics (i.e., shared code and data). It offers an asynchronous, task-based interface for efficient interaction between AAMs. Just like applications are built from AAMs, even the OS itself consists of AAMs that are interfaced by applications via asynchronous messages instead of synchronous system calls. A dedicated OS component, which is aware of all AAMs in the system, is responsible for dynamic and exclusive allocation of cores to AAMs depending on their current workload. Thus, cores rarely switch between heterogeneous workloads of different AAMs. And, at the same time, frequent switches between homogeneous tasks become fast, local operations of an AAM, which do not involve the OS kernel. In this paper, we describe shortcomings of existing operating systems, our new system design concept, and present evaluation results of our prototype implementation.. slides

Invited Talk, Xidian University, June 21/22, 2019: Machine Learning Approaches for Efficient Design Space Exploration of Application-specific NoCs

Prof. Dr.-Ing. Ulf Schlichtmann and Dr.-Ing. Li Zhang (Chair of Electronic Design Automation, TUM)

The photo shows Li Zhang and Ulf Schlichtmann together with Prof. Yintang Yang, Vice President of Xidian University, with some of his colleagues.

Dr.-Ing. Li Zhang and Prof. Ulf Schlichtmann (TUM) visited Xidian University in Xi’an, China on June 21/22, 2019, for discussions about research collaborations. On June 22, Prof. Schlichtmann gave an overview on the research of the TUM’s Chair for Electronic Design Automation – which of course includes the InvasIC research – as well as a dedicated talk on "Machine Learning Approaches for Efficient Design Space Exploration of Application-specific NoCs". Despite the talk happening on a Saturday, it was attended by more than 125 participants. The talk was followed by a very lively discussion. Dr. Li Zhang had already visited Xidian University earlier in January 2019 and given a talk on her timing-related research which she performed in the context of TRR 89.

Keynote Talk, ARCS 2019, May 20-23, 2019 Predictability Issues in Operating Systems

Prof. Dr.-Ing. Wolfgang Schröder-Preikschat (Distributed Systems and Operating Systems, FAU)

Prof. Dr.-Ing. Wolfgang Schröder-Preikschat gave an invited keynote talk at the 32nd International Conference on Architecture of Computing Systems (ARCS 2019) in Copenhagen, Denmark. Predictability is always subject to the underlying assumptions being made. For real-time systems, time response of processes in relation to the strictness of deadlines is of particular importance. With an additional focus on embedded systems, space and energy requirements become relevant as well and need to be considered in combination. As far as software is concerned, structure and organisation of the programs to be executed determines whether or not predictable processes will take place in a given computing system. Design for predictability is an overarching aspect that crosscuts the whole computing system and particularly addresses operating systems. This talk was about structuring principles of non-sequential programs - in the shape of but not limited to operating systems - to abet predetermination of quality attributes of non-sequential (real-time) processes, it is not about analytical methods to effectively predetermine these attributes. Issues in operating systems as to timing, space, and energy requirement are touched. Emphasis thereby is on coordination of cooperation and competition between processes, namely synchronisation. It is shown how measures of process synchronisation against the background of many-core processors cater to these issues. more information

Invited Talk, ACM International Conference on Computing Frontiers 2019, April 30, 2019: Anytime Instructions for Programmable Accuracy Floating-Point Arithmetic

Marcel Brand, Michael Witterauf, PD Dr.-Ing. Frank Hannig and Prof. Dr.-Ing. Jürgen Teich (Hardware/Software Co-Design, FAU)

Marcel Brand held a talk on the paper "Anytime Instructions for Programmable Accuracy Floating-Point Arithmetic".

Many embedded applications strive for high performance and power efficiency but rely on latency-intensive floating-point operations. This expensiveness can be offset, for example, by approximate and mixed-precision floating-point computation. In this paper, we present a novel concept called anytime instructions. Anytime instructions explicitly specify the number of result bits that are calculated at full precision. After presenting the basics of anytime instructions, we apply this novel concept to floating-point division by presenting an anytime division functional unit that is implemented in a VLIW processor. In this setup, we show the effectiveness of anytime instructions in iterative computations. We show a latency improvement of 54.8 % for computing 53 iterations of the Babylonian method for square-root calculation while not sacrificing the accuracy of the final square-root result. more information

Inaugural lecture: "(Viel-)Kern-Vielfalt hilft viel – aber wie?"

April 26, 2019, Erlangen (FAU): PD Dr.-Ing. Frank Hannig (FAU) will give his inaugural lecture on "(Viel-)Kern-Vielfalt hilft viel – aber wie?" at "Tag der Informatik". more information

Best Presentation Award April 19, 2019, Montreal, Canada:

Simon Schuster (FAU)

Simon Schuster received the Best Presentation Award for his presentation on the paper "Proving Real-Time Capability of Generic Operating Systems by System-Aware Timing Analysis" contributed by Simon Schuster, Peter Wägemann, Peter Ulbrich, and Prof. Dr.-Ing. Wolfgang Schröder-Preikschat (FAU) at RTAS 2019. more information

Invited Talk, The University of Tokyo, April 18, 2019: Multi-Core Computing with Timing, Reliability, and Security Guarantees

Prof. Dr.-Ing. Jürgen Teich (Hardware/Software Co-Design, FAU)

In this talk, we gave an overview of novel techniques for systematically mapping applications to NoC-based multi-core architectures (MPSoCs). Complex applications requiring heterogenous processing resources are often described by task graphs with data dependencies. Here, the nodes represent actors or tasks which are typically activated periodically based on the availability of data. One prominent domain of applications fitting this model is stream processing. Here, it is often important to guarantee either bandwidth or execution time requirements. But more recently, also security, energy and reliability aspects impose constraints on the mapping of the tasks as well as their communication to cores, respectively routes in the underlying NoC. In the context of mapping methodologies, we first present a class of algorithms that perform "Self-Embedding". The idea is here that a source node issues a request to find appropriate resources to embed its sucessor tasks, and so on. The next class of techniques introduced is called "Hybrid Application Mapping (HAM)". Here, a careful analysis and characterization of symmetric mappings by constellations of cores and routes is explored in a static (compile-time) phase called "Design Space Exploration (DSE)". At run-time, the operating system then only needs to search within such pre-analysed constellations for finding a concrete mapping that will satisfy the given non-functional constraints by construction. We presented ideas of how timing constraints may be statically analysed in case of compositional MPSoC architectures such that deadlines or throughput requirements will be automatically met for streaming applications. Finally, we concluded with a discussion on resource constellations that may satisfy certain security requirements on an MPSoC.

Prof. Dr.-Ing. Jürgen Teich (Hardware/Software Co-Design, FAU) visited the University of Tokyo and gave an invited talk at the department of creative informatics.

Invited Talk, International Symposium on Applied Reconfigurable Computing (ARC 2019), April 10, 2019: Hybrid Prototyping for Manycore Design and Validation

Leonard Masing, Fabian Lesniak and Prof. Dr.-Ing. Jürgen Becker (ITIV, KIT)

The trend towards more parallelism in information processing is unbroken. Manycore architectures provide both massive parallelism and flexibility, yet they raise the level of complexity in design and programming. Prototyping of such architectures helps in handling this complexity by evaluating the design space and discovering design errors. Several system simulators exist but they can only be used for early software development and interface specification. FPGA-based prototypes on the other hand are restricted by available FPGA resources or expensive multi-FPGA prototyping platforms. We present a hybrid prototyping approach for manycore systems that consists of an FPGA-part and a virtual part of the architecture on a host system. The hybrid prototyping requires less FPGA resources while retaining its speed advantage and enabling flexible modeling in the virtual platform. We describe the concept, provide an analysis of timing accuracy and synchronization of the FPGA with the Virtual Platform (VP) and show an example in which the hybrid prototype is used for feature development and evaluation of a scientific manycore architecture. The hybrid prototype allows us to evaluate a 7x7 architecture on a Virtex-7 XC7VX485T FPGA board which otherwise could only fit a reduced 2x2 design of our architecture. more information

Design, Automation and Test in Europe (DATE) 2019, March 25-29, 2019:

DATE combines the world’s favourite electronic systems design and test conference with an international exhibition for electronic design, automation and test, from system-level hardware and software implementation right down to integrated circuit design. It took place at the Firenze Fiera in Florence, Italy from 25 to 29 March 2019. The DATE 2019 Conference and Exhibition attracted more than 1,600 registrations from over 40 countries and concluded with excellent feedback from both participants and exhibitors.

Impressions from DATE 2019. (photographs DATE 2019 / © Cruz Garcia)

On Monday, the DATE week started with five in-depth technical tutorials on the main topics of DATE as well as a hands-on industry tutorial given by leading experts in their respective fields. The topics covered Machine Learning for Manufacturing and Test, OpenCL Design Flows for FPGAs, Approximate Computing, Hardware-based Security, and Safety and Security in Automotive, while the hands-on tutorial was on Quantum Computing with IBM Q and Qiskit. Prof. Jürgen Teich had the honour to be General Chair of DATE 2019 and opened the conference on Tuesday. During the Opening Ceremony, plenary keynote lectures were given by Astrid Elbe, Managing Director of Intel Labs Europe, and Jürgen Bortolazzi, Director Driver Assistance Systems and Highly Automated Driving at Porsche. Furthermore, a talk by Claudio Giorgione, Curator of the Leonardo Department at the National Museum of Science and Technology Milano, gave insight into life and work of Leonardo da Vinci in line with the 500th anniversary of his death, which is celebrated in Florence in 2019.

Impressions from DATE 2019. (photographs DATE 2019 / © Cruz Garcia)

The main conference programme from Tuesday to Thursday included 58 technical sessions organized in parallel tracks from the four areas D – Design Methods & Tools A – Application Design T – Test and Dependability E – Embedded and Cyber-physical Systems and from several special sessions on Hot Topics, such as Emerging Design Technologies, Design and Test of Secure Systems, IoT Security, Embedded Systems for Deep Learning, Augmented Living and Personalized Healthcare, Robotics and Industry 4.0, as well as results and lessons learned from European projects. Two Special Days in the programme focused on areas bringing new challenges to the system design community. On Wednesday, the keynote on the topic of heterogeneous, high-scale computing in the era of cloud-connected devices by David Pellerin, Amazon US, was the highlight of the special day on “Embedded Meets Hyperscale and HPC”. During the Special Day on “Model-Based Design of Intelligent Systems” on Thursday, Edward Lee from UC Berkeley took “A Fundamental Look at Models and Intelligence” in his keynote.

Impressions from DATE 2019. (photographs DATE 2019 / © Cruz Garcia)

One of the highlights of the DATE week was the DATE Party and took place in the Palazzo Borghese, which is located in the heart of Firenze and is a beautiful example of neoclassic architecture. Local delights, entertaining music and a visit by Leonardo da Vinci made this evening a memorable event on its own!

Further impressions from DATE 2019. (photographs DATE 2019 / © Cruz Garcia)

On Friday, 10 full-day workshops covered several hot topics from areas like (a) Open Source and Machine Learning in EDA, (b) Emerging Techniques for Memories, Interconnections, and Quantum Computing, (c) Hardware Design, Synthesis, and Approximate Computing, as well as EDA in application domains such as (d) Autonomous Systems and IoT. Furthermore, an International F1/10 Autonomous Racing Demo took place, supported by IEEE CEDA. This presentation of open-source, affordable and high-performance 1/10 scale autonomous vehicles was a particular highlight on the last day of DATE 2019. more information

Exhibition Theatre Session at DATE 2019, March 25-29, 2019:

Prof. Dr.-Ing. Jürgen Teich, General Chair of DATE 2019 organised an Exhibition Theatre Session on “DFG Collaborative Funding Instruments” on 26 March with an associated exhibition of selected currently funded collaborative research initiatives which ran for three days (Tuesday – Thursday). The session was chaired by German Research Foundation (DFG) program director Dr. Andreas Raabe who started with an introduction of which types of collaborative funding instruments are offered in Germany, but also funding opportunities for international cooperations. After this introduction, concrete initiatives in the scope of topics of DATE were shortly introduced and summarized by representatives with a majority of these initiatives also exhibiting during the conference week. Two Priority Programs (SPP1648 Software for Exascale Computing and SPP2037 Scalable Data Management for Future Hardware), three Collaborative Research Centres (SFB 901 On-the-fly Computing, SFB 912 Highly Adaptive Energy Efficient Computing and SFB 876 Providing Information by Resource-Constrained Data Analysis) and the Transregional Research Centre TRR 89 Invasive Computing, as well as the Research Unit FOR 1800 (Controlling Concurrent Change – Towards Self-Aware Automotive And Space Vehicles) and a Bi-National Research Project (Conquering MPSOC Complexity with Principles of a Self-Aware Information) used the opportunity to present newest ideas, work-in-progress and lessons learned from the project.

Impressions from the Exhibition Theatre Session at DATE 2019. (photographs DATE 2019 / © Cruz Garcia)

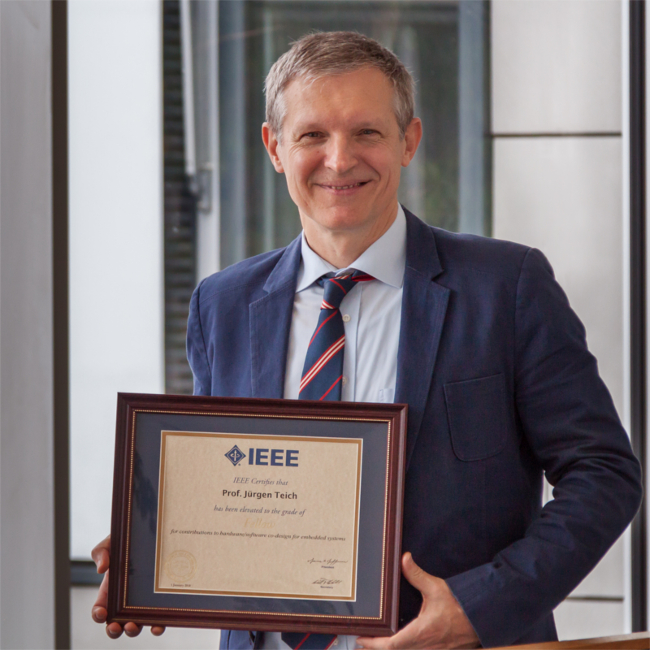

Prof. Dr.-Ing. Jürgen Teich Awarded at DATE 2019, March 25-29, 2019:

Prof. Dr.-Ing. Jürgen Teich (Hardware/Software Co-Design, FAU)

Prof. Dr.-Ing. Jürgen Teich was honoured with the IEEE CS TTTC Outstanding Service Award at the Design, Automation and Test in Europe 2019 (DATE) in recognition of significant service as DATE 2019 General Chair.

DATE 2019 / © Cruz Garcia

Tobias Schwarzer Awarded at DATE 2019, March 25-29, 2019:

Tobias Schwarzer (Hardware/Software Co-Design, FAU)

Tobias Schwarzer received the PhD Forum Best Poster Prize at DATE 2019 for his poster titled "System-Level Mapping and Synthesis of Data Flow-Oriented Applications on MPSoCs". The prize is supported by EDAA, ACM Sigda and IEEE CEDA.

Tobias Schwarzer receiving the PhD Forum Best Poster Prize at DATE 2019 in Florence. (photographs DATE 2019 / © Cruz Garcia)

Workshop "Scheduling Meets Fixed-Parameter Tractability", Februrary 4-8, 2019:

Prof. Dr. Nicole Megow (UB), Matthias Mnich and Gerhard Woeginger

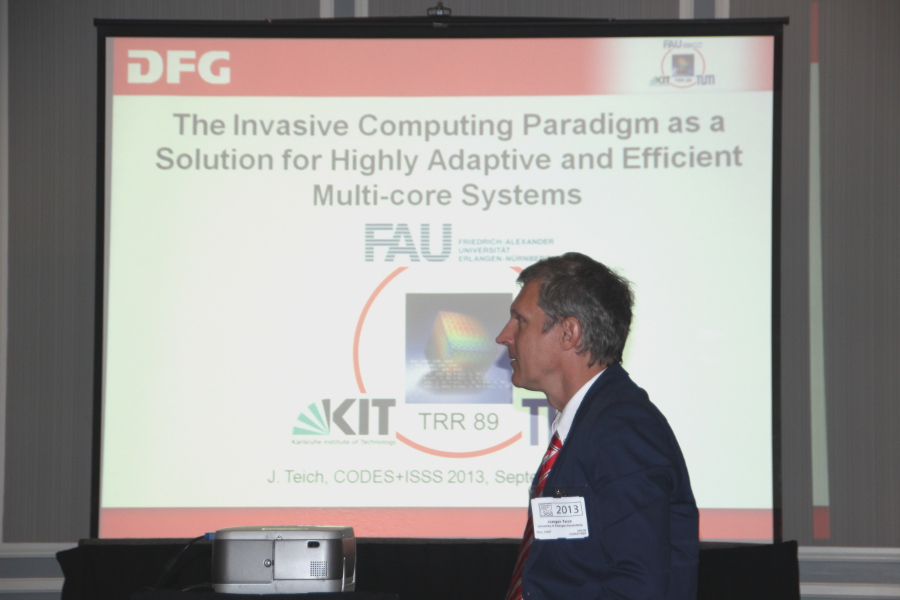

Prof. Dr. Nicole Megow organised at Lorentz Center Leiden the workshop "Scheduling Meets Fixed-Parameter Tractability". more information