C2: Simulation of Invasive Applications and Invasive Architectures

Principal Investigators:

Dr. Hannig, Prof. Gerndt, Prof. Herkersdorf

Scientific Researchers:

Vahid Lari, Marcel Meyer, Sascha Roloff, Thomas Wild, Aurang Zaib

Abstract

Subproject C2 investigates novel simulation methodologies that enable the validation and variants' exploration of all essential features of invasive computing in order to guide research directions at an early project stage. C2 has two major research fields: (a) Behavioural simulation of invasive resource-aware programs. (b) Simulation of different types of invasive architectures in a uniform methodology. In order to handle the complexity and diversity of considered architectures as well as different invasive programming, resource management, and invasion strategies, we will develop new methods for the modularisation and orthogonalisation of these exploration concerns.

Synopsis

Invasive computing is a hotbed for a new computing paradigm including research in theory, programming languages and applications as well as architectural design. In order to explore different invasive architectures, invasion strategies, and invasive programming approaches, subproject C2 will research novel simulation methodologies and their implementation. Accordingly, this subproject has a fundamental role within the transregional collaborative research centre (TCRC) by providing evaluation facilities and by assisting in the optimisation of the concepts across all project areas, especially, without the need to have full hardware or software implementations available. To cope with these challenges, subproject C2 is subdivided into two main research areas, (a) behavioural simulation of invasive applications and (b) simulation of invasive architectures.

The main idea of the behavioural simulation methodology is to design a consistent approach that provides the main commands of invasion (invade, infect, etc.) and offers the possibility to emulate a rudimentary invasive architecture. Providing such a methodology offers verification possibilities and can significantly speed up research in areas A and D on a generic invasive architecture. The development will be synchronised with the research of subproject A1 on the concrete language for invasive computing. The construction of the behavioural simulation methodology will most likely be based on the language X10.

The second main objective is a uniform simulation methodology, which should be based on common methods to model invasive applications, common mechanisms to provide resource-awareness and will allow to integrate different architectural simulators across all hardware architectures covered in the TCRC. We plan to develop a very flexible and modular simulation approach that is able to cover different levels of detail and time resolutions, considering various purposes of simulation such as concept demonstration, exploration, or dimensioning of system variants. Here, we intend to develop a novel and unique layered approach that separates the invasion control from the actual architectural simulation. Compared to a monolithic concept, this layered approach will allow to fulfil different requirements and enable the independent modification of aspects relevant to application designers, operating system engineers and hardware architects. Thus, an orthogonalisation of different concerns (e. g., invasive programming approaches, resource management and invasion strategies, different invasive hardware architectures or even heterogeneous compositions of them) will be feasible. In addition, the approach allows taking advantage of state-of-the-art simulation techniques for complex multi-processor systems as much as possible and thus directs the research to the new concepts raised by invasive computing.

The final goal of the subproject is to develop a prototype of a simulation environment that allows to simulate variants of tightly-coupled processor arrays, loosely-coupled MPSoCs and HPC clusters. Furthermore, the environment should provide interfacing capabilities to investigate invasive resource management strategies and monitoring concepts.

Approach

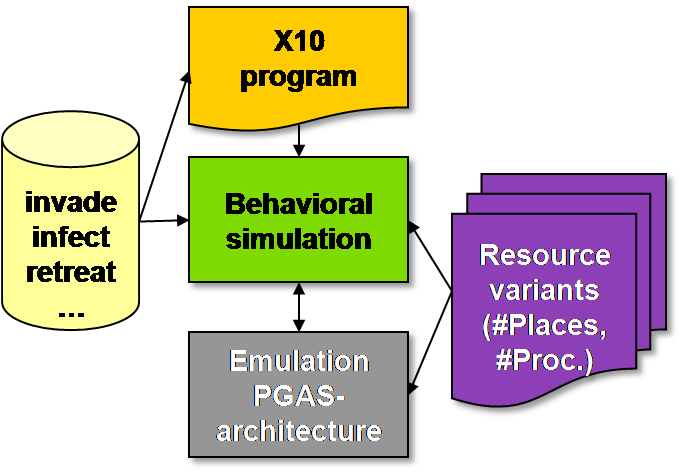

The image below shows the approach for the behavioural simulation of invasive applications. There, an application is written in the X10 programming language and makes use of the framework of invasive programming in order to express their resource-aware demands. This framework is also realized via a library-based approach in X10. The behavioral simulator provides means to describe the target architecture in terms of number and topology of tiles and their containing processing elements and local memory sizes. It simulates the execution of several applications running on the simulated target architecture and provides resource-aware functional correctness.

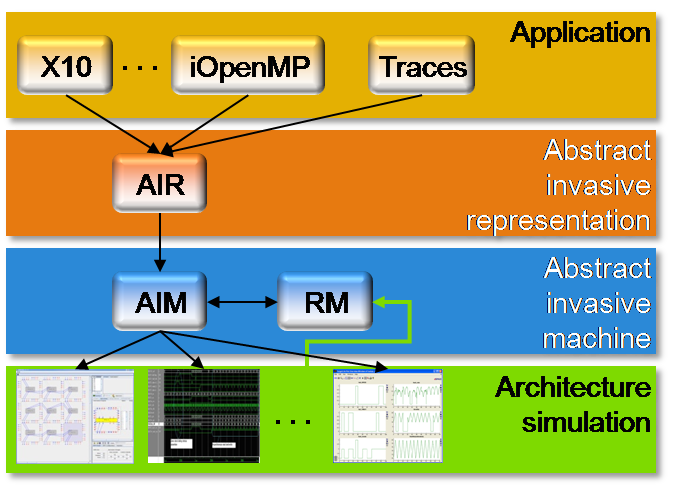

The next picture shows the approach for the simulation of invasive architectures. It is structured into four layers and provides an integrated invasive simulation framework. That means that several architectural simulators specific to a certain target architecture are combined together into only one integrated simulator.

InvadeSIM

As part of project C2, a functional simulator called InvadeSIM was developed. This simulator enables the simulation of invasive applications on configurable invasive architectures. Visualization tools help to analyze the behaviour of the invasive application in terms of resource reservation and utilization. The following all-in-one package contains the simulator, visualization tools, and invasive X10 example applications. Currently, we only support one platform, there will be more supported in later releases.

A tutorial and a README file are part of the package and explain the prerequisites and the usage of the simulator. For a small introduction of the usage of the simulator, the following video tutorial is provided:

Publications

| [1] | Nidhi Anantharajaiah, Tamim Asfour, Michael Bader, Lars Bauer, Jürgen Becker, Simon Bischof, Marcel Brand, Hans-Joachim Bungartz, Christian Eichler, Khalil Esper, Joachim Falk, Nael Fasfous, Felix Freiling, Andreas Fried, Michael Gerndt, Michael Glaß, Jeferson Gonzalez, Frank Hannig, Christian Heidorn, Jörg Henkel, Andreas Herkersdorf, Benedict Herzog, Jophin John, Timo Hönig, Felix Hundhausen, Heba Khdr, Tobias Langer, Oliver Lenke, Fabian Lesniak, Alexander Lindermayr, Alexandra Listl, Sebastian Maier, Nicole Megow, Marcel Mettler, Daniel Müller-Gritschneder, Hassan Nassar, Fabian Paus, Alexander Pöppl, Behnaz Pourmohseni, Jonas Rabenstein, Phillip Raffeck, Martin Rapp, Santiago Narváez Rivas, Mark Sagi, Franziska Schirrmacher, Ulf Schlichtmann, Florian Schmaus, Wolfgang Schröder-Preikschat, Tobias Schwarzer, Mohammed Bakr Sikal, Bertrand Simon, Gregor Snelting, Jan Spieck, Akshay Srivatsa, Walter Stechele, Jürgen Teich, Furkan Turan, Isaías A. Comprés Ureña, Ingrid Verbauwhede, Dominik Walter, Thomas Wild, Stefan Wildermann, Mario Wille, Michael Witterauf, and Li Zhang. Invasive Computing. FAU University Press, August 16, 2022. [ DOI ] |

| [2] | Sascha Roloff, Frank Hannig, and Jürgen Teich. Modeling and Simulation of Invasive Applications and Architectures. Springer, May 2019. [ DOI ] |

| [3] | Sascha Roloff. Modeling and Simulation of Invasive Applications and Architectures. Dissertation, Hardware/Software Co-Design, Department of Computer Science, Friedrich-Alexander-Universität Erlangen-Nürnberg, Germany, July 19, 2018. |

| [4] | Oliver Reiche. A Domain-Specific Language Approach for Designing and Programming Heterogeneous Image Systems. Dissertation, Hardware/Software Co-Design, Department of Computer Science, Friedrich-Alexander-Universität Erlangen-Nürnberg, Germany, July 5, 2018. |

| [5] | Éricles R. Sousa, Michael Witterauf, Marcel Brand, Alexandru Tanase, Frank Hannig, and Jürgen Teich. Invasive computing for predictability of multiple non-functional properties: A cyber-physical system case study. In Proceedings of the 29th Annual IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP). IEEE, July 2018. [ DOI ] |

| [6] | Andreas Weichslgartner, Stefan Wildermann, Michael Glaß, and Jürgen Teich. Invasive Computing for Mapping Parallel Programs to Many-Core Architectures. Springer, January 15, 2018. [ DOI ] |

| [7] | Michael Witterauf, Frank Hannig, and Jürgen Teich. Constructing fast and cycle-accurate simulators for configurable accelerators using C++ templates. In Proceedings of the 28th International Symposium on Rapid System Prototyping (RSP), pages 9–15. ACM, October 2017. [ DOI ] |

| [8] | Sascha Roloff, Frank Hannig, and Jürgen Teich. High performance network-on-chip simulation by interval-based timing predictions. In Proceedings of the 15th IEEE/ACM Symposium on Embedded Systems for Real-time Multimedia (ESTIMedia), pages 2–11. ACM, October 2017. [ DOI ] |

| [9] | Jürgen Teich. Invasive computing – editorial. it – Information Technology, 58(6):263–265, November 24, 2016. [ DOI ] |

| [10] | Vahid Lari, Andreas Weichslgartner, Alex Tanase, Michael Witterauf, Faramarz Khosravi, Jürgen Teich, Jürgen Becker, Jan Heißwolf, and Stephanie Friederich. Providing fault tolerance through invasive computing. it – Information Technology, 58(6):309–328, October 19, 2016. [ DOI ] |

| [11] | Stefan Wildermann, Michael Bader, Lars Bauer, Marvin Damschen, Dirk Gabriel, Michael Gerndt, Michael Glaß, Jörg Henkel, Johny Paul, Alexander Pöppl, Sascha Roloff, Tobias Schwarzer, Gregor Snelting, Walter Stechele, Jürgen Teich, Andreas Weichslgartner, and Andreas Zwinkau. Invasive computing for timing-predictable stream processing on MPSoCs. it – Information Technology, 58(6):267–280, September 30, 2016. [ DOI ] |

| [12] | Jürgen Teich, Michael Glaß, Sascha Roloff, Wolfgang Schröder-Preikschat, Gregor Snelting, Andreas Weichslgartner, and Stefan Wildermann. Language and compilation of parallel programs for *-predictable MPSoC execution using invasive computing. In Proceedings of the 10th IEEE International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), pages 313–320, Lyon, France, September 2016. [ DOI ] |

| [13] | Vahid Lari. Providing fault tolerance through invasive computing. Talk at DTC 2016, The Munich Workshop on Design Technology Coupling, Munich, Germany, June 30, 2016. |

| [14] | Sascha Roloff, Alexander Pöppl, Tobias Schwarzer, Stefan Wildermann, Michael Bader, Michael Glaß, Frank Hannig, and Jürgen Teich. ActorX10: An actor library for X10. In Proceedings of the 6th ACM SIGPLAN X10 Workshop (X10), pages 24–29. ACM, June 14, 2016. [ DOI ] |

| [15] | Sascha Roloff, Frank Hannig, and Jürgen Teich. InvadeSIM: A simulator for heterogeneous multi-processor systems-on-chip. Tool Presentation at the University Booth at Design, Automation and Test in Europe (DATE), Dresden, Germany, March 2016. [ .pdf ] |

| [16] | Alexandru Tanase, Michael Witterauf, Éricles R. Sousa, Vahid Lari, Frank Hannig, and Jürgen Teich. LoopInvader: A compiler for tightly coupled processor arrays. Tool Presentation at the University Booth at Design, Automation and Test in Europe (DATE), Dresden, Germany, March 2016. [ .pdf ] |

| [17] | Vahid Lari. Invasive Tightly Coupled Processor Arrays. Springer Singapore, 2016. [ DOI ] |

| [18] | Vahid Lari. Invasive Tightly Coupled Processor Arrays. Dissertation, Hardware/Software Co-Design, Department of Computer Science, Friedrich-Alexander-Universität Erlangen-Nürnberg, Germany, November 18, 2015. |

| [19] | Vahid Lari, Jürgen Teich, Alexandru Tanase, Michael Witterauf, Faramarz Khosravi, and Brett H. Meyer. Techniques for on-demand structural redundancy for massively parallel processor arrays. Journal of Systems Architecture (JSA), 61(10):615–627, November 2015. [ DOI ] |

| [20] | Frank Hannig and Andreas Herkersdorf. Introduction to the special issue on testing, prototyping, and debugging of multi-core architectures. Journal of Systems Architecture, 61(10):600, November 7, 2015. [ DOI ] |

| [21] | Sascha Roloff, Stefan Wildermann, Frank Hannig, and Jürgen Teich. Invasive computing for predictable stream processing: A simulation-based case study. In Proceedings of the 13th IEEE Symposium on Embedded Systems for Real-time Multimedia (ESTIMedia). IEEE, October 2015. [ DOI ] |

| [22] | Alexandru Tanase, Michael Witterauf, Jürgen Teich, Frank Hannig, and Vahid Lari. On-demand fault-tolerant loop processing on massively parallel processor arrays. In Proceedings of the 26th IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP), pages 194–201. IEEE, July 2015. [ DOI ] |

| [23] | Sascha Roloff, David Schafhauser, Frank Hannig, and Jürgen Teich. Execution-driven parallel simulation of PGAS applications on heterogeneous tiled architectures. In Proceedings of the 52nd ACM/EDAC/IEEE Design Automation Conference (DAC), pages 44:1–44:6. ACM, June 2015. [ DOI ] |

| [24] | Vahid Lari, Alexandru Tanase, Jürgen Teich, Michael Witterauf, Faramarz Khosravi, Frank Hannig, and Brett H. Meyer. A co-design approach for fault-tolerant loop execution on coarse-grained reconfigurable arrays. In Proceedings of the 2015 NASA/ESA Conference on Adaptive Hardware and Systems (AHS), pages 1–8. IEEE, June 2015. [ DOI ] |

| [25] | Frank Hannig and Jürgen Teich, editors. Proceedings of the First Workshop on Resource Awareness and Adaptivity in Multi-Core Computing (Racing 2014). May 2014. [ arXiv ] |

| [26] | Aurang Zaib, Prashanth Raju, Thomas Wild, and Andreas Herkersdorf. A layered modeling and simulation approach to investigate resource-aware computing in mpsocs. In Proceedings of the First Workshop on Resource Awareness and Adaptivity in Multi-Core Computing (Racing 2014), pages 51–56, May 2014. [ arXiv ] |

| [27] | Vahid Lari, Alexandru Tanase, Frank Hannig, and Jürgen Teich. Massively parallel processor architectures for resource-aware computing. In Proceedings of the First Workshop on Resource Awareness and Adaptivity in Multi-Core Computing (Racing 2014), pages 1–7, May 2014. [ arXiv ] |

| [28] | Sascha Roloff, Frank Hannig, and Jürgen Teich. Towards actor-oriented programming on PGAS-based multicore architectures. In Workshop Proceedings of the 27th International Conference on Architecture of Computing Systems (ARCS). VDE Verlag, February 2014. |

| [29] | Frank Hannig, Vahid Lari, Srinivas Boppu, Alexandru Tanase, and Oliver Reiche. Invasive tightly-coupled processor arrays: A domain-specific architecture/compiler co-design approach. ACM Transactions on Embedded Computing Systems (TECS), 13(4s):133:1–133:29, 2014. [ DOI ] |

| [30] | Jörg Henkel, Vijaykrishnan Narayanan, Sri Parameswaran, and Jürgen Teich. Run-time adaptation for highly-complex multi-core systems. In Proceedings of the IEEE International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), September 2013. [ DOI ] |

| [31] | Sascha Roloff, Andreas Weichslgartner, Jan Heißwolf, Frank Hannig, and Jürgen Teich. NoC simulation in heterogeneous architectures for PGAS programming model. In Proceedings of the 16th International Workshop on Software and Compilers for Embedded Systems (M-SCOPES), pages 77–85. ACM, June 2013. [ DOI ] |

| [32] | Frank Hannig. Resource-aware computing on domain-specific accelerators. In Proceedings of the 10st Workshop on Optimizations for DSP and Embedded Systems (ODES), page 35. ACM, February 24, 2013. Keynote. [ DOI ] |

| [33] | Vahid Lari, Shravan Muddasani, Srinivas Boppu, Frank Hannig, Moritz Schmid, and Jürgen Teich. Hierarchical power management for adaptive tightly-coupled processor arrays. ACM Transactions on Design Automation of Electronic Systems (TODAES), 18(1):2:1–2:25, January 2013. [ DOI ] |

| [34] | Frank Hannig. Why do we see more and more domain-specific accelerators in multi-processor systems? Guest Lecture at University of California, Riverside in CS 287 Colloquium in Computer Science, Riverside, CA, USA, November 9, 2012. |

| [35] | Frank Hannig. Invasive tightly-coupled processor arrays. Talk, 1st International Workshop on Domain-Specific Multicore Computing (DSMC) at International Conference on Computer-Aided Design (ICCAD), San Jose, CA, USA, November 8, 2012. |

| [36] | Michael Gerndt, Frank Hannig, Andreas Herkersdorf, Andreas Hollmann, Marcel Meyer, Sascha Roloff, Josef Weidendorfer, Thomas Wild, and Aurang Zaib. An integrated simulation framework for invasive computing. In Proceedings of the Forum on Specification and Design Languages (FDL), pages 209–216. IEEE, September 2012. |

| [37] | Sascha Roloff, Frank Hannig, and Jürgen Teich. Simulation of resource-aware applications on heterogeneous architectures. In Proceedings of the 8th International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (ACACES), pages 127–130, July 2012. |

| [38] | Vahid Lari, Shravan Muddasani, Srinivas Boppu, Frank Hannig, and Jürgen Teich. Design of low power on-chip processor arrays. In Proceedings of the 23rd IEEE International Conference on Application-specific Systems, Architectures, and Processors (ASAP), pages 165–168. IEEE Computer Society, July 2012. [ DOI ] |

| [39] | Sascha Roloff, Frank Hannig, and Jürgen Teich. Fast architecture evaluation of heterogeneous MPSoCs by host-compiled simulation. In Proceedings of the 15th International Workshop on Software and Compilers for Embedded Systems (SCOPES), pages 52–61. ACM Press, May 2012. [ DOI ] |

| [40] | Sascha Roloff, Frank Hannig, and Jürgen Teich. Approximate time functional simulation of resource-aware programming concepts for heterogeneous MPSoCs. In Proceedings of the 17th Asia and South Pacific Design Automation Conference (ASP-DAC), pages 187–192, January 2012. [ DOI ] |

| [41] | Vahid Lari, Srinivas Boppu, Shravan Muddasani, Frank Hannig, and Jürgen Teich. Hierarchical power management for adaptive tightly-coupled processor arrays. Talk, International Workshop on Adaptive Power Management with Machine Intelligence at International Conference on Computer-Aided Design (ICCAD), San Jose, CA, USA, November 10, 2011. |

| [42] | Vahid Lari, Andriy Narovlyanskyy, Frank Hannig, and Jürgen Teich. Decentralized dynamic resource management support for massively parallel processor arrays. In Proceedings of the 22nd IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP), pages 87–94. IEEE Computer Society, September 2011. [ DOI ] |

| [43] | Jürgen Teich. Programming invasively parallel – an introduction. Pervasive Parallelism Laboratory (PPL) Seminar Talk, Stanford University, CA, USA, July 25, 2011. |

| [44] | Jürgen Teich. Invasive parallel computing – an introduction. Par Lab and AMP Lab Seminar Talk, UC Berkeley, CA, USA, July 22, 2011. |

| [45] | Frank Hannig, Sascha Roloff, Gregor Snelting, Jürgen Teich, and Andreas Zwinkau. Resource-aware programming and simulation of MPSoC architectures through extension of X10. In Proceedings of the 14th International Workshop on Software and Compilers for Embedded Systems (SCOPES), pages 48–55. ACM Press, June 2011. [ DOI ] |

| [46] | Vahid Lari, Frank Hannig, and Jürgen Teich. Distributed resource reservation in massively parallel processor arrays. In Proceedings of the International Parallel and Distributed Processing Symposium Workshops (IPDPSW), pages 318–321. IEEE Computer Society, May 2011. [ DOI ] |

| [47] | Jürgen Teich, Jörg Henkel, Andreas Herkersdorf, Doris Schmitt-Landsiedel, Wolfgang Schröder-Preikschat, and Gregor Snelting. Invasive computing: An overview. In Michael Hübner and Jürgen Becker, editors, Multiprocessor System-on-Chip – Hardware Design and Tool Integration, pages 241–268. Springer, Berlin, Heidelberg, 2011. [ DOI ] |

| [48] | Frank Hannig. Retargetable mapping of loop programs on coarse-grained reconfigurable arrays. Talk, International Conference on Hardware-Software Codesign and System Synthesis (CODES+ISSS), Scottsdale, AZ, USA, October 26, 2010. |

| [49] | Jürgen Teich. Invasive computing – basic concepts and foreseen benefits. Artist Network of Excellence on Embedded System Design Summer School Europe 2010, Autrans, France, Invited Tutorial, September 7, 2010. |

| [50] | Farhadur Arifin, Richard Membarth, Amouri Abdulazim, Frank Hannig, and Jürgen Teich. FSM-controlled architectures for linear invasion. In Proceedings of the 17th IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC), pages 59–64, October 2009. [ DOI ] |

| [51] | Jürgen Teich. Invasive algorithms and architectures. it - Information Technology, 50(5):300–310, 2008. |